# Understanding MSP430 Flash Data Retention

MSP430 Applications

# ABSTRACT

The MSP430<sup>™</sup> microcontrollers (MCUs) offer both read-only memory (ROM)-based and flash-based devices. Understanding the MSP430 flash is extremely important for efficient, robust, and reliable system design. Data retention is one of the key aspects to flash reliability. In this application report, data retention for the MSP430 flash is discussed in detail and the effect of temperature is given primary importance. The concepts discussed in this document are applicable to all MSP430 MCUs that are flash based in any memory configuration.

#### Contents

| 1 | Introdu                      | uction                  | 2 |

|---|------------------------------|-------------------------|---|

| 2 | MSP430 Flash Characteristics |                         | 2 |

|   | 2.1                          | Flash Programming       | 2 |

|   |                              | Flash Failure Mechanism |   |

|   | 2.3                          | Flash Data Retention    | 3 |

| 3 | Conclu                       | usion                   | 9 |

#### List of Figures

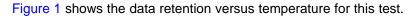

| 1 | Flash Data Retention vs Temperature for 170°C 420-Hour Test | 5 |

|---|-------------------------------------------------------------|---|

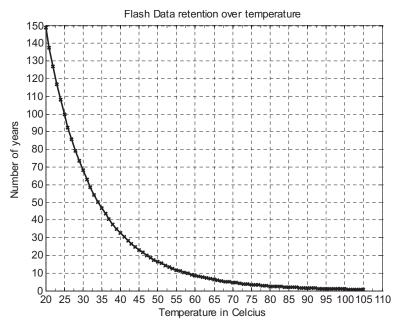

| 2 | Bake Time and Temperature Increased to 500 Hours at 250°C   | 6 |

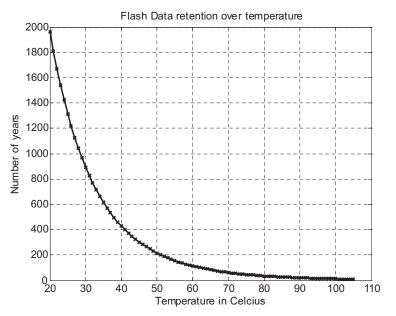

| 3 | Bathtub Curve for Failures                                  | 7 |

### **Trademarks**

MSP430 is a trademark of Texas Instruments. All other trademarks are the property of their respective owners.

### 1 Introduction

Memory in general is broadly classified as read-only memory (ROM) or random-access memory (RAM). These two types behave differently, and each has its own set of merits and demerits. Flash memory is a hybrid of ROM and RAM, inheriting the best features of both types of memories. Flash memory, driven by low cost, is electrically programmable, fast to read from, exhibits high density, and is nonvolatile. Flash memory is usually stacked as sectors and can be erased only as sectors. For the MSP430 MCUs, each sector of the main memory flash is 512 bytes in length. Because the flash memory is electrically programmable, it requires a sufficient voltage to erase and program efficiently. This voltage must be maintained during the entire flash erase and write to ensure reliability of the operation. This topic is discussed in detail in the following section. The other limitation of flash is the number of writes and erases, which has a direct impact on flash wear out. Tips to ensure flash longevity and factors that contribute to flash failure are discussed in this application report.

Data retention can be one of the primary concerns at extreme temperatures. In this application report, emphasis is given to basics of flash data retention, factors that influence this parameter, and the various figures of merit to interpret flash data retention, along with tips to prevent failures on MSP430 MCUs.

# 2 MSP430 Flash Characteristics

The thick-oxide split-gate cell design used in the MSP430 has several advantages in terms of data retention and endurance performance compared to other flash cell architectures such as thin-oxide stacked-gate or thin-oxide two-transistor cell designs. It is easier to manufacture and less susceptible than thin-oxide designs to manufacturing defects that relate to data retention loss over time.

# 2.1 Flash Programming

The erase state of every bit in flash is logic 1. It is important and recommended that the user perform an erase operation before a write (program) operation to any location in MSP430 flash. Most of the MSP430 MCUs shipped from the factory have their main memory completely erased, while information memory might contain factory test data.

### 2.1.1 Programming Tips

This section gives a few external and internal tips that should be followed to minimize adverse effects during system design. Failure to adhere to any of these tips can result in unreliable flash write or erase and lead to unpredictable flash behavior.

#### Internal Considerations

Efficient programming of the MSP430 flash is governed by two major requirements: supply voltage (DVCC) and the flash timing generator clock ( $f_{FTG}$ ). For the MSP430F1xx and most of the MSP430F4xx family of devices, the supply voltage must be a minimum of 2.7 V. The minimum supply voltage is reduced to 2.2 V and 1.8 V for the MSP430F2xx family and MSP430F5xx families, respectively. Particularly in battery-powered applications, battery capacity must be sufficient to meet the minimum operating voltage and currents necessary for in-application program and erase. The  $f_{FTG}$  for MSP430F1xx, MSP430F2xx, and MSP430F4xx devices must be in the range of 257 kHz  $\leq f_{FTG} \leq 476$  kHz, while it is generated internally on the MSP430F5xx devices. There is a practical limit on the number of flash erase and write cycles for every MSP430 MCU, which is in the range of 100000 cycles.

#### **External Considerations**

Use of a programming adapter that has been certified to meet the MSP430 flash programming specifications greatly reduces the risk of a flash failure. Regular inspection for wear out of the programming socket also ensures better performance over time. If in-circuit programming is done via JTAG or boot loader, the programming operation should be performed at the end of the manufacturing cycle. Mechanical and thermal process steps, such as encapsulation mold cure, should be completed before programming.

Verification is an important step if flash integrity must be checked. A checksum routine can be called on a regular basis for critical applications. In some of the MSP430F2xx, MSP430F4xx, and MSP430F5xx devices, the marginal read mode is implemented to facilitate a checksum routine. Checksum routine values with and without this feature are compared to find weak programming flash locations on the MCU. Different values can indicate a violation of one or more of the above mentioned programming considerations.

# 2.2 Flash Failure Mechanism

This section describes a few intrinsic and extrinsic failure mechanisms of flash memory. Although these mechanisms are applicable to any industry flash, they apply to the MSP430 flash as well. Several tests are in place to ensure that each MSP430 MCU that leaves the factory does not show any of the following symptoms.

# **Charge Retention**

Charge retention is the ability of the flash cell to retain its programmed value during long-term storage. If there are defects in the dielectrics or the substrate, charges can move to or from the floating gate, causing elevated charge loss. Also, with sufficient thermal activation, all bits could lose their charge. Analyses indicate that this failure mechanism occurs well beyond the normal lifetime of the device. Charge retention is discussed more in Section 2.3.

### **Oxide Degradation**

The high fields used during program and erase can result in increased low field leakage through the dielectrics of the cell. This can increase the susceptibility to charge loss of the cell. Analyses and long-term storage results have verified that the post-cycling retention performance of the cells extends well beyond normal lifetimes.

# **Program and Erase Time Degradation**

After a large number of write or erase cycles, a high charge can be trapped in the dielectrics surrounding the floating gate. This charge can decrease the effective field across the cell during program and erase operations, increasing the time required to complete the program and erase operations. Data on TI flash cells has shown that the erase and program time walk-out is well beyond normal use conditions.

### Write Disturb

During the program operation, high fields are placed not only on the bit being programmed, but on other bits along the same word line or bit line. If there are defects in the dielectrics or in the substrate, leakage paths can be created, so inadvertent programming of a non-selected bit can be observed. To address this defect mechanism, high-voltage screens are in place in the test program to eliminate such units from the population.

These are some of the failure mechanisms that could occur to any flash, and tests are place to for screen out any MSP430 MCUs that might have them.

# 2.3 Flash Data Retention

Data retention of any flash is the ability to retain its programmed state. Flash data retention is known to degrade over temperature. Various tests and methods are in place to determine the reliability of flash. This application report mainly addresses the concept of accelerated test and the use of statistics to predict reliability.

# 2.3.1 Accelerated Tests

To test the flash data retention at various temperatures we make use of accelerated tests on the flash. These tests are wholly based on Arrhenius law and equation. The Arrhenius theory allows the test of any device under accelerated environments for short periods and predicts the behavior under normal conditions for longer periods. Similar tests are performed on the MSP430 flash to test and predict data retention. During each test, an unprogrammed device is subjected to these tests. A flash failure is indicated when any of the flash cells change from an unprogrammed state (logic 1) to logic 0.

(1)

(3)

Equation 1 shows the Arrhenius equation.

$$AF = e^{-\frac{E_a}{k} \left(\frac{1}{T_2} - \frac{1}{T_1}\right)}$$

where

- AF = Acceleration factor

- Ea = Activation energy (0.6 eV for data retention)

- k = Boltzmann's constant (8.623 x 10<sup>-5</sup> eV/K)

- T1 = Application junction temperature in Kelvin

- T2 = Accelerated stress junction temperature in Kelvin

Depending on AF, a back calculation using the Arrhenius equation for any desired temperature leads to fairly accurate data-retention times.

# 2.3.1.1 Infant Mortality Test During Production

This test is not a flash data retention test, rather, it is performed to screen out infant mortality among devices during production. It is an accepted theory that all devices statistically follow a bathtub curve when it comes to failures. The infant mortality failures would fall into the left hand slope of the bath tub curve. Under this test, all of the MSP430 MCUs are baked for 24 hours or 72 hours (depending on device family).

# 2.3.1.2 Flash Data Retention Tests During Qualification

To determine the flash data retention, further tests are conducted during qualification of the MSP430 MCUs. Two cases are explained in this section for different temperature and baking time.

# 2.3.1.3 Case 1: 420-Hour Baking Time at 170°C

In this test, the MSP430 MCU is continuously subjected to this high temperature of 170°C for 420 hours. The purpose of this test is to determine data retention at higher temperatures, and then calculate expected data retention at 25°C using Equation 2.

Using  $T1 = 25^{\circ}C$  and  $T2 = 170^{\circ}C$  in Equation 1 gives the following AF:

$$AF = e^{\frac{-E_a}{k} \left( \frac{1}{170^{\circ}C + 273} - \frac{1}{25^{\circ}C + 273} \right)} = AF = e^{\frac{-0.6}{8.623 \times 10^{-5}} \left( \frac{1}{443} - \frac{1}{298} \right)} = 2085$$

(2)

Using this AF information, back substitution gives the data retention in years at 25°C (see Equation 3).

Data\_retention<sub>years\_at\_25°C</sub> =  $\frac{420 \times 2085}{24 \times 365} \approx 100$  years

After this value has been established, different AF values can be calculated for different T2 temperatures. Similar back substitution yields data retention in years.

Figure 1. Flash Data Retention vs Temperature for 170°C 420-Hour Test

The corner cases for 85°C and 105°C are slightly over 2 years and less than 9 months, respectively. These numbers do not truly indicate the performance of the MSP430 flash. To qualify the MSP430 MCU to have better data retention, further tests are conducted on the MSP430 flash.

There are instances in which there are strict requirements for flash data retention, particularly when the device is subjected to extreme temperatures. Although, in almost all cases, the device would never be subject to extreme temperatures 24 hours a day, 7 days a week, tests are in place to achieve better numbers at the corner case temperatures. To improve data retention for corner case temperatures, bake time must be increased. One such approach is to fix the bake temperature and use Equation 1 to establish bake time for the requirements on data retention. The bake temperature has been increased from case 1 to a temperature of 250°C. This test is performed on the flash used in the MSP430 MCU.

Table 1 lists the values plotted in Figure 1.

| Temperature (°C) | Data Retention (Years) |

|------------------|------------------------|

| 20               | 148.912                |

| 25               | 100                    |

| 30               | 68.006                 |

| 35               | 46.843                 |

| 40               | 32.652                 |

| 45               | 23.02                  |

| 50               | 16.406                 |

| 55               | 11.814                 |

| 60               | 8.591                  |

| 65               | 6.307                  |

| 70               | 4.672                  |

| 75               | 3.491                  |

| 80               | 2.63                   |

| 85               | 1.997                  |

| 90               | 1.528                  |

(5)

| Temperature (°C) | Data Retention (Years) |  |  |

|------------------|------------------------|--|--|

| 95               | 1.178                  |  |  |

| 100              | 0.914                  |  |  |

| 105              | 0.714                  |  |  |

Table 1. Case 1 Results (continued)

# 2.3.1.4 Case 2: 500-Hours Baking Time at 250°C

Putting these parameters into Equation 1, the AF is calculated as shown in Equation 4.

$$AF = e^{\frac{-E_a}{k} \left( \frac{1}{250^{\circ}C + 273} - \frac{1}{25^{\circ}C + 273} \right)} = AF = e^{\frac{-0.6}{8.623 \times 10^{-5}} \left( \frac{1}{523} - \frac{1}{298} \right)} = 23044$$

(4)

This value indicates the huge effect baking temperature has on flash data retention. The AF is almost ten times higher, implying that the data retention numbers would significantly improve.

Similarly, data retention at 25°C is calculated in Equation 5.

Data\_retention<sub>years\_at\_25°C</sub> =

$$\frac{500 \times 23044}{24 \times 365} \approx 1315$$

years

Figure 2 shows the data retention versus temperature.

Figure 2. Bake Time and Temperature Increased to 500 Hours at 250°C

This data qualifies the device to almost 10 years at the extreme temperature of 105°C and nearly 27 years at 85°C.

Case 1 and Case 2 discussed one method of interpretation of flash data retention. In Section 2.3.2, the statistical measure of flash data retention is discussed.

Table 2 lists the data plotted in Figure 2.

| Temperature (°C) | Data Retention (Years) |

|------------------|------------------------|

| 20               | 1959.187               |

| 25               | 1315.313               |

| 30               | 894.733                |

| 35               | 616.298                |

Table 2. Case 2 Results

| Temperature (°C) | Data Retention (Years) |

|------------------|------------------------|

| 40               | 429.597                |

| 45               | 302.872                |

| 50               | 215.853                |

| 55               | 155.432                |

| 60               | 113.033                |

| 65               | 82.979                 |

| 70               | 61.466                 |

| 75               | 45.926                 |

| 80               | 34.599                 |

| 85               | 26.272                 |

| 90               | 20.102                 |

| 95               | 15.493                 |

| 100              | 12.024                 |

| 105              | 9.395                  |

#### Table 2. Case 2 Results (continued)

#### 2.3.2 Reliability Tests

In general, reliability is defined as the probability that a device or a system will perform a required task under stated conditions for a stated period of time. The chosen functionality under specific conditions can be predicted with a good degree of confidence with this measure. For the present subject, the functionality is flash data retention, and the conditions are changes in temperature. In general, failure in devices follows a bathtub curve shown in Figure 3. The curve can be divided into three regions of interest: infant mortality, normal life of operation, and wear-out phase. The chances of failures are higher during infant mortality and the wear-out phase and almost a negligible constant during normal life of operation. In Section 2.3.1, screening out devices that fall under the infant mortality part of the curve was mentioned.

Time

Figure 3. Bathtub Curve for Failures

#### MSP430 Flash Characteristics

www.ti.com

The interpretation of test results to indicate the reliability of a device requires the definition and understanding of a few key parameters. A brief introduction to these terminologies follows:

#### Failure Rate ( $\lambda$ )

Failure rate is the number of failures per unit time. It follows the bathtub curve of Figure 3.

#### Failure-In-Time (FIT) Rate

FIT is a direct measure of failure rate in 10<sup>9</sup> device hours or the number of devices that failed after 10<sup>9</sup> hours. It is inversely proportional to number of devices tested and the duration of the tests.

### **Acceleration Factor (AF)**

AF is an outcome of an accelerated life test done on the device to predict its long-term performance. Its role in the Arrhenius equation was shown in previous sections. This factor also contributes inversely to the FIT.

#### **Confidence Level (CL)**

CL is the probability level estimated based on sample tests conducted for failures. It also is a confidence in the integrity of numbers used to determine the failure rate. It follows a chi-square ( $\chi^2$ ) distribution and depends on the number of failures. In most cases, the confidence level is chosen to be 60% or 90%. It directly contributes to the FIT.

#### Mean Time Between Failures (MTBF)

MTBF is the inverse of the FIT for a repairable device and is a classic measure of reliability of a system or of a product. It is figure that goes through constant update with number of samples tested and failed.

### Reliability [R(t)]

R(t) is defined for fixed time periods to predict the number of devices that would perform reliably. It is a byproduct of the FIT and expressed as a percentage.

From this point on, it is a simple task of putting these numbers in their respective formulas to get reliability data. Section 2.3.2.1 and Section 2.3.2.2 show examples for the tests discussed in Section 2.3.1.

### 2.3.2.1 Example 1

Consider the test conducted in Case 1 for MSP430 flash with the temperature set to 170°C for a time of 420 hours. The sample size is 240 and the AF, FIT, and MTBF are shown for confidence levels of 60% and 90%.

The AF is still calculated using Equation 1 for each temperature in question (see Equation 6):

$$AF = e^{\frac{-E_a}{k} \left(\frac{1}{170^{\circ}C + 273} - \frac{1}{30^{\circ}C + 273}\right)} = AF = e^{\frac{-0.6}{8.623 \times 10^{-5}} \left(\frac{1}{443} - \frac{1}{303}\right)} = 1418$$

where

• H = Time for which the device is tested for in hours = 420

N = Number of devices = 240

$$FIT = \frac{\frac{\chi^2}{2} \times 10^9}{N \times H \times AF}$$

The value of  $\chi^2/2$  for confidence levels of 0.6 and 0.9 from the  $\chi^2$  distribution gives a value of 0.916 and 2.305 respectively. The FIT is therefore calculated as shown in Equation 7 and Equation 8:

$$FIT_{30^{\circ}C,0.6CL} = \frac{\frac{\chi^2}{2} \times 10^9}{N \times H \times AF} = \frac{0.916 \times 10^9}{240 \times 420 \times 1418} = 6.41$$

$$FIT_{30^{\circ}C,0.9CL} = \frac{\frac{\chi^2}{2} \times 10^9}{N \times H \times AF} = \frac{2.305 \times 10^9}{240 \times 420 \times 1418} = 16.13$$

(8)

The FIT numbers are expressed in number of parts failing per billion units, as indicated by the 10<sup>9</sup> factor.

(6)

2)

(14)

9

When the FIT numbers are known, it is easy to calculate the MTBF defined by Equation 9, Equation 10, and Equation 11:

$$MTBF_{years} = \frac{1}{FIT \times 24 \times 365} \times 10^9$$

(9)

$$MTBF_{years,30^{\circ}C,0.6CL} = \frac{1}{FIT_{30^{\circ}C,0.6CL} \times 24 \times 365} \times 10^{9} = \frac{1}{6.41 \times 24 \times 365} \times 10^{9} = 17809 \text{ years}$$

(10)

$$MTBF_{years,30^{\circ}C,0.9CL} = \frac{1}{FIT_{30^{\circ}C,0.9CL} \times 24 \times 365} \times 10^{9} = \frac{1}{16.13 \times 24 \times 365} \times 10^{9} = 7077 \text{ years}$$

(11)

#### 2.3.2.2 Example 2

If the reliability for a fixed period of time needs to be calculated for a device, Equation 12 can be used:

$R(t) = e^{-t} MTBF$

\_20 /

where

In combination with Example 1, a problem statement can be derived to determine the reliability of a device that is constantly subjected to a single temperature for a set period of time. Suppose t is defined as 20 years and the MTBF for 30°C was used (from Example 1) with confidence levels of 0.6 and 0.9, the reliability is calculated as shown in Equation 13 and Equation 14:

$$R_{30^{\circ}C,0.6CL}(t) = e^{-t} MTBF = e^{-20} (17809) = 0.9988 = 99.88\%$$

$$R_{30^{\circ}C,0.9CL}(t) = e^{-t} MTBF = e^{-20} (7077) = 0.9971 = 99.71\%$$

(14)

These results indicate the reliability of the MSP430 flash data retention devices at a fixed temperature and time. If Case 2 results were used in Example 1 and Example 2, the numbers obtained for MTBF and reliability would be even better.

#### Conclusion 3

This application report has addressed the means to understand data retention for the MSP430 flash. Various tests performed on the MSP430 MCU that truly reflected flash data retention in number of years were described. Statistical measures were introduced to understand the MSP430 MCU performance. Examples showed how MTBF numbers can be used to calculate reliability of an MSP430 MCU under various conditions influenced by temperature.

Revision History

www.ti.com

# **Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes from March 27, 2008 to August 24, 2018 |                                                                                    | age |

|------------------------------------------------|------------------------------------------------------------------------------------|-----|

| •                                              | Editorial and format changes throughout document                                   | . 1 |

| •                                              | Changed the bake times in Section 2.3.1.1, Infant Mortality Test During Production | . 4 |

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2018, Texas Instruments Incorporated