# ABSTRACT

This technical User's Guide describes the hardware architecture of the AM65x IDK. The AM65x processor is part of the K3 Multicore SoC architecture platform Arm.

# **Table of Contents**

| 1 Introduction                                                 | 2               |

|----------------------------------------------------------------|-----------------|

| 1.1 Key Features                                               |                 |

| 2 AM65x IDK Overview                                           |                 |

| 3 Common Processor Board                                       |                 |

| 3.1 Key Features                                               | 7               |

| 3.2 Functional Block Diagram                                   | 9               |

| 3.3 Overview of Common Processor Board                         | 9               |

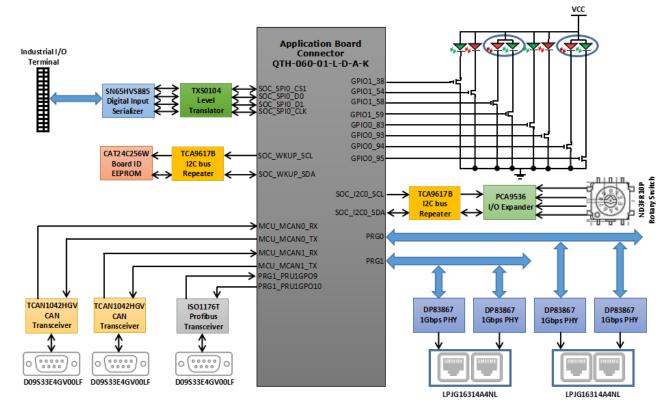

| 4 IDK Application Card                                         | 56              |

| 4.1 Key Features                                               | 56              |

| 4.2 Overview of IDK Application Board                          | 57              |

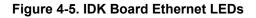

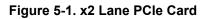

| 5 x2 Lane PCIe Personality Card                                | 68              |

| 5.1 Key Features                                               | <mark>68</mark> |

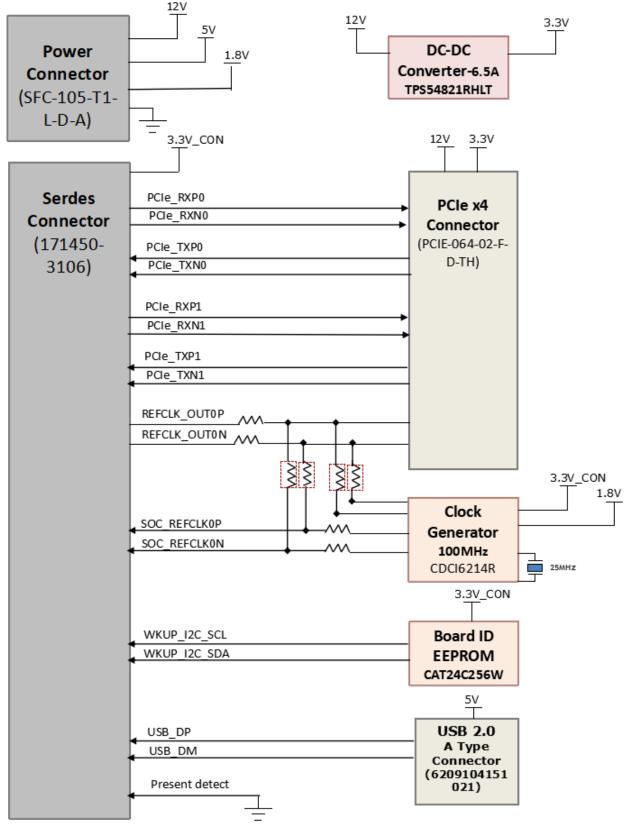

| 5.2 Overview of PClex2 Daughter Card                           | <mark>69</mark> |

| 6 Known Issues                                                 | 72              |

| 6.1 Determining the Revision and Date Code for the EVM         | 72              |

| 6.2 Known Issues for the A, E4, and E3 Revision                | 72              |

| 6.3 Known Issues for the E4 & E3 Revision                      | 72              |

| 6.4 Known Issues for the E3 Revision                           | 72              |

| 7 Configuring the PRG0 and PRG1 Ethernet Interface to MII      | 75              |

| 7.1 Ethernet PHY Initial Conditions and TX Clock Signal Change | 75              |

| 7.2 Ethernet PHY and TX Data Signals Change                    | 82              |

| 8 Revision History                                             | <mark>85</mark> |

# 1 Introduction

The AM65x IDK is a standalone test, development, and evaluation module (EVM) system that lets developers write software and develop hardware for industrial communication-type applications. The IDK is equipped with AM6548 processor from TI and a defined set of features to let the user experience industrial communication solutions using serial, Ethernet-based, PCIe, and many other interfaces. Using standard interfaces, the IDK can communicate with other processors or systems, and act as a communication gateway. In addition, the IDK can directly operate as a standard remote I/O system or simple sensor connected to an industrial communication network. The embedded emulation logic allows for emulation and debugging using standard development tools such as Code Composer Studio<sup>™</sup>, from TI, by using the supplied USB cable.

# 1.1 Key Features

The AM65x IDK is a high performance, standalone development platform that enables users to evaluate and develop industrial applications for the Texas Instrument's K3 System-on-Chip (SoC). The AM65x IDK supports the following key features:

- Based on the K3 architecture with Arm

- 4-GB DDR4 supporting data rate up to 1600 MT/s

- 16-GB eMMC Flash

- Full size SD card, up to 64-GB density with UHS-1 support (8-GB UHS-1 card supplied with the kit)

- 128-Mbit SPI EEPROM

- 512-Mbit OSPI EEPROM

- 256-Kbit I2C Boot EEPROM

- 3× PRU-ICSSG, supporting multi-protocol industrial Gigabit Ethernet with up to 6 ports

- 1x MCU Gigabit Ethernet port

- One USB2.0 interface port with Micro AB connector

- CSI-2 connector to interface camera card

- · I-PEX EVAFLEX5-VS connector to interface with the LCD adapter card

- · GPMC/DSS interface expansion connector

- Application board expansion connector

- SERDES expansion connector to interface two lane PCIe Personality card

- XDS110 on-board emulator

- Quad port UART to USB circuit over microB USB connector

- Expansion headers:

- Two UART

- One SPI

- One I2C

- Four timer signals

- Boot mode selection using DIP switches

- Two push buttons to generate interrupts

- Industrial Ethernet LEDs

- Rotary switch input

- Two CAN interface terminated to DB-9 connector

- Digital serializer for processing wide range inputs from industrial I/O connector

- Profibus UART transceiver terminated with DB9 connector

- DC Input: 11 V to 28 V

- Status output: LEDs to indicate power status

- INA devices for current monitoring

- · Over- and under-voltage protection circuit

- RoHS-compliant design

Featured applications:

- Industrial Drives

- Industrial Sensors

• Factory Automation and Control

# 2 AM65x IDK Overview

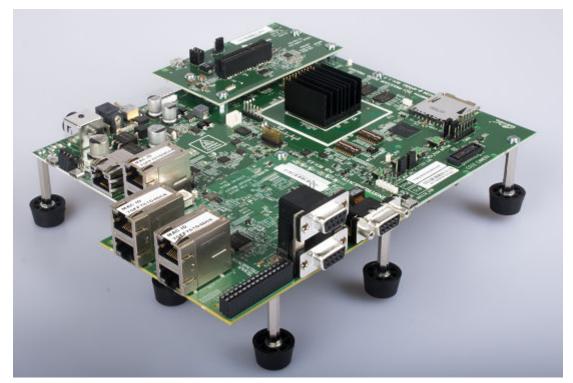

Figure 2-1. System Assembly Image

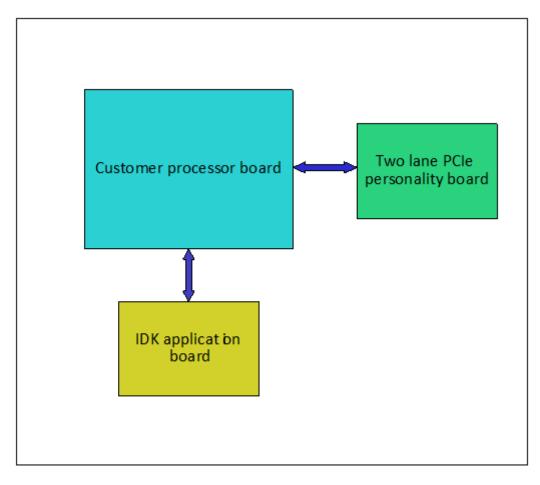

Figure 2-2 shows the overall architecture of AM65x IDK.

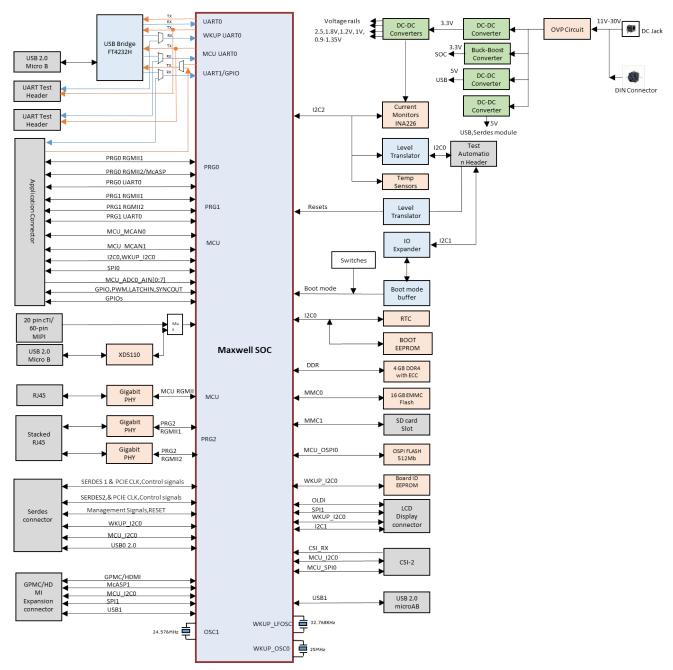

# Figure 2-2. System Architecture Interface

The AM65x IDK consists of a common processor board, IDK application board, and a two-lane PCIe personality card. Detailed descriptions of these cards are explained in the following sections.

# **3 Common Processor Board**

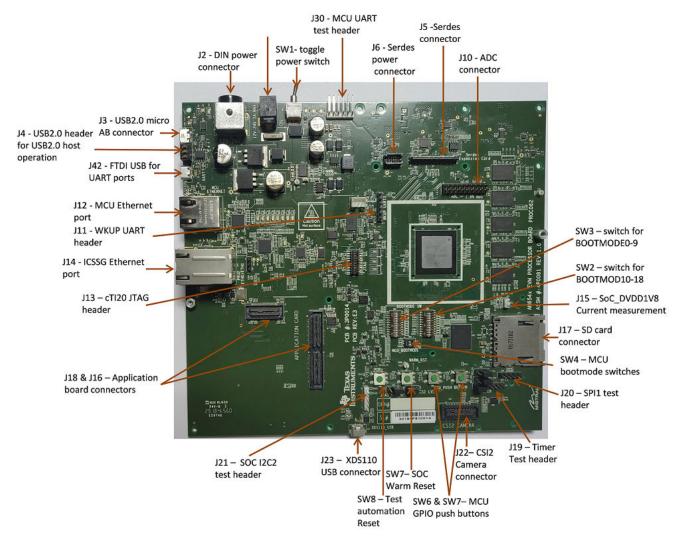

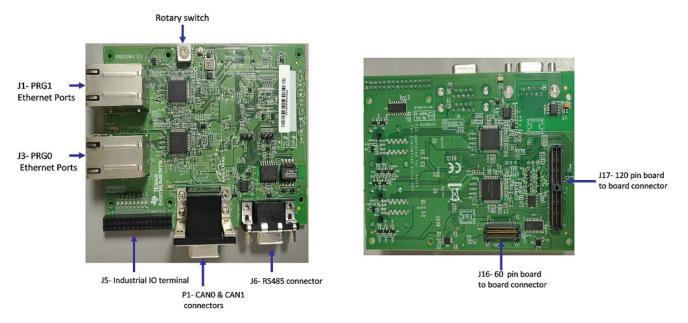

Figure 3-1. Top View of the Common Processor Board

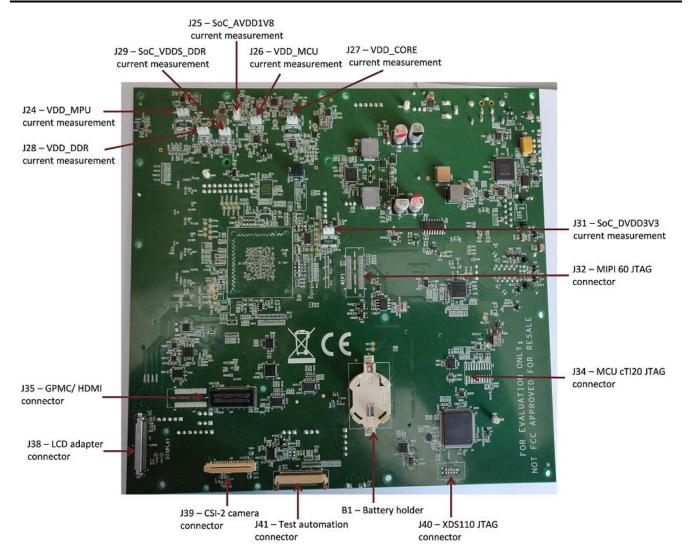

Figure 3-2. Bottom View of the Common Processor Board

# 3.1 Key Features

# SoC:

- Based on the K3 architecture with Quad-Core Arm<sup>®</sup> Cortex<sup>®</sup>-A53 Microprocessor and Dual-Core Arm Cortex-R5F Arm

- Heatsink and support for 12-V fan

# Memory:

- 4-GB DDR4 supporting data rate up to 1600 MT/s

- 16-GB eMMC Flash which can support HS400 speed of operation

- · Full size SD card, up to 64-GB density with UHS-1 support

- 128-Mbit SPI EEPROM

- 512-Mbit OSPI EEPROM

- 256-Kbit I2C EEPROM for Boot

# I/O Interface:

- One MCU Gigabit Ethernet port and two Industrial Ethernet ports based on the Gigabit Industrial Communication Subsystem (PRU-ICSS-Gb) paired with Texas Instruments Gigabit Ethernet PHYs

- One USB2.0 interface with Micro AB connector

- CSI-2 connector to interface camera card

# Expansion Bus:

- I-PEX EVAFLEX5-VS connector to interface with the LCD adapter card

- GPMC/DSS interface expansion connector for secondary display

- · Application connector to expansion application cards

- SERDES expansion connector to support various SERDES modules

# Debug:

- XDS110 on-board emulator

- Supports 20-pin JTAG connection from external emulator

- Automatic selection between on-board and external emulator (higher priority)

- Quad port UART to USB circuit over microB USB connector

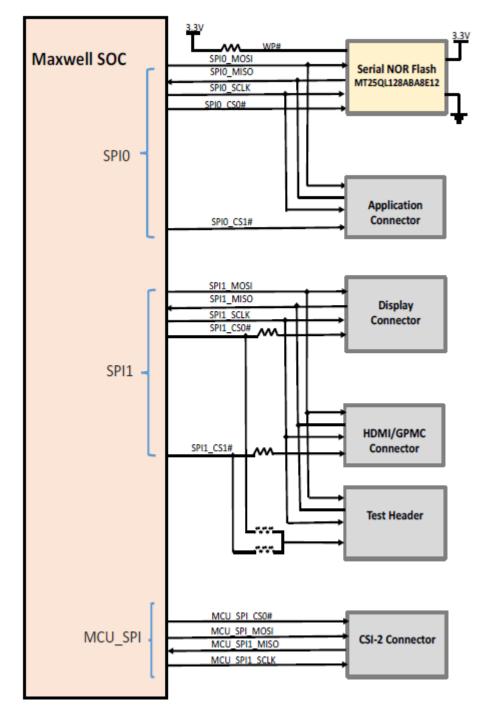

- Two UART, one SPI, and I2C ports connected to test header for slave testing of the AM65x device

- · Four timer signals from Maxwell connected to test header

- Two push buttons to generate Interrupts

# Power Supply:

- Wide range DC input: 11 V to 28 V

- Status output: LEDs to indicate power status

- INA devices for current monitoring

- Over- and under-voltage protection circuit

# Compliance:

- RoHS-compliant

- REACH-compliant

In compliance with the Article 33 provision of the EU REACH regulation, we are notifying you that this module includes crystals (ABM3-25.000MHZ-D2Y-T, ABM3-12.000MHZ-D2Y-T) from Abracon LLC that contains two Substance of Very High Concern (SVHC) above 0.1%. These uses from Texas Instruments do not exceed 1 ton per year. The SVHC's are Diboron trioxide CAS#1303-86-2 and Lead Oxide CAS# 1317-36-8.

# 3.2 Functional Block Diagram

The functional block diagram of the common processor board is shown in Figure 3-3.

# **3.3 Overview of Common Processor Board**

This section provides an overview of the different interfaces and circuits on the common processor board.

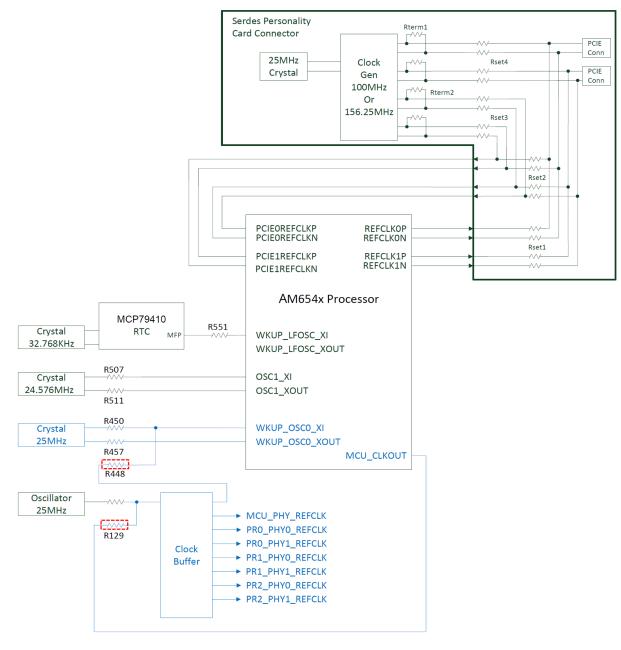

# 3.3.1 Clocking

SOC requires a crystal for MCU, System Clock, and a 32.768-kHz square wave input for LFOSC input.

# 3.3.1.1 RTC Clock

A real time clock IC is connected to the I2C0 interface of the AM65x processor. The RTC device is powered by 3.3 V as a primary supply. This IDK is designed for optional use with a removable CR2032 UL recognized lithium

battery, which can be inserted using a battery holder provided on the CP board. Always use the CR2032VP Energizer 3-V Lithium coin cell battery or similar CR2032 UL-recognized battery with nominal voltage of 3.0 V, Capacity 240 mAh. The battery is not provided with the IDK EVM. A 32.768-kHz quartz crystal is used to provide the clock for the RTC device. The RTC device generates 32.768-kHz square wave output, which is connected to WKUP\_LFOSC input of the SoC.

Figure 3-4. AM65x IDK Clock Tree

Note

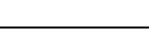

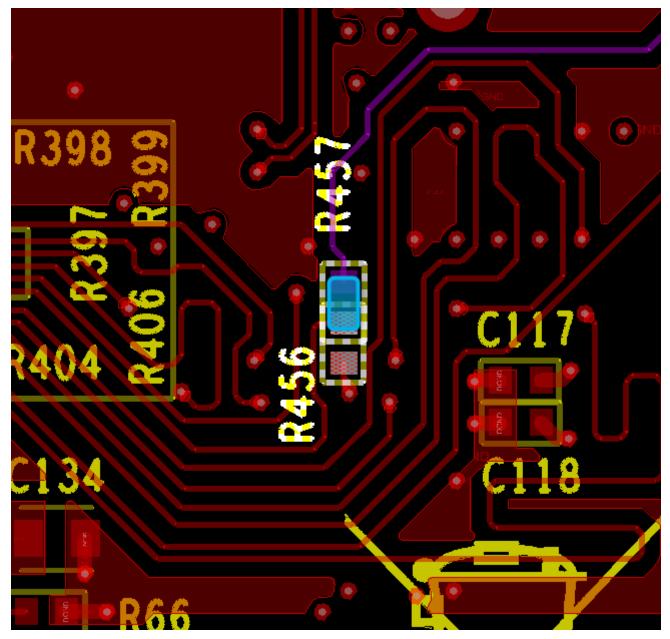

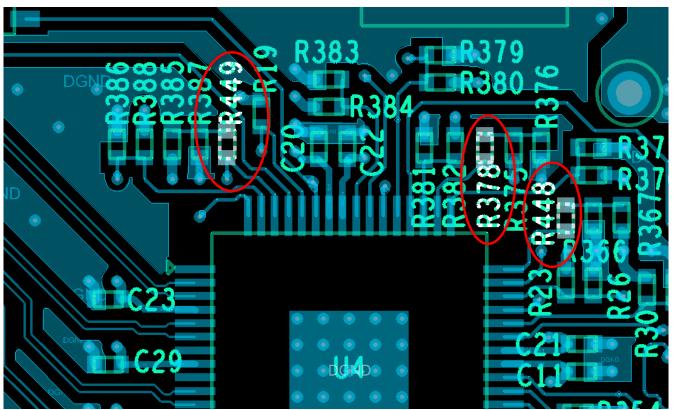

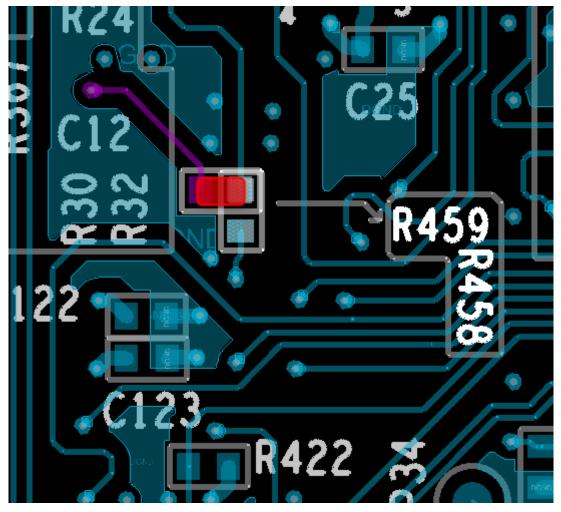

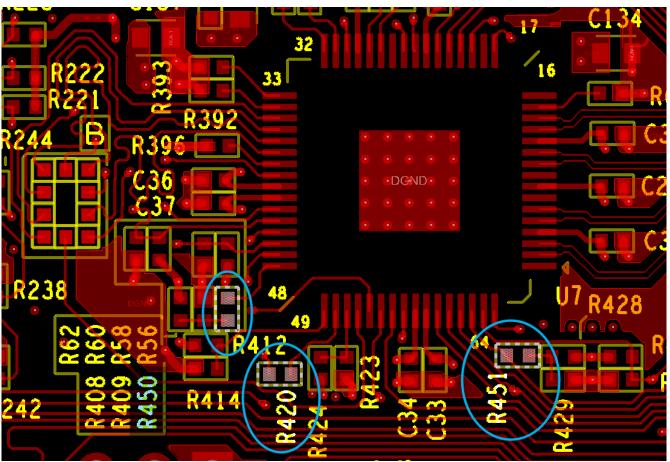

Resistors marked with a red color box are DNI.

# 3.3.1.2 Maxwell SoC Clock

HFOSC0, HFOSC1: The HFOSC0 (OSC0) and HFOSC1 (OSC1) clocks are muxed inside the SOC, and the result is connected to main PLL. The output of the main PLL is used as the system clock for SOC. The input of WKUP\_OSC 0 can be provided with a 25-Mhz crystal or by using the output of the clock generator. The default

25-Mhz crystal is connected; to use the clock generator output as input for WKUP\_OSC 0, resistor R448 must be mounted and resistors R450 and R457 removed.

LFOSC: The 32.768-KHz square wave is provided by the MFP output of the RTC component.

# 3.3.1.3 Ethernet PHY Clocks

The Ethernet PHYs are clocked with 25 MHz using a 1:10 LVCMOS clock generator. It is a clock buffer, which takes 25-MHz crystal/LVCMOS reference input and provides ten 25-MHz LVCMOS clock outputs.

The source for the clock buffer can be either the MCU\_CLKOUT0 signal from the AM65x processor or a 25-MHz oscillator (default). This selection can be made through the select lines of the clock buffer by using the resistor options as shown in Table 3-1. In addition, the pinmux for pin AB3 must be modified to select the MCU\_CLKOUT0 function. This function is not present when the part is removed from reset. If MCU\_CLKOUT0 is used, the Ethernet boot mode for the AM645x cannot be used.

### Note

When MCU\_CLKOUT0 is used as the source for the clock buffer, resistor R129 must be mounted.

| Table 3-1. Source Clock Selection for the Clock Buffer |   |               |            |            |  |  |

|--------------------------------------------------------|---|---------------|------------|------------|--|--|

| IN_SEL1 IN_SEL0 clock chosen Mount Unmount             |   |               |            |            |  |  |

| 0                                                      | 0 | MCU clock     | R187, R197 | R189, R193 |  |  |

| 1                                                      | 0 | Crystal input | R189, R197 | R187, R193 |  |  |

# 3.3.1.4 SERDES Clock

The SERDES reference clock inputs and outputs of the SoC are routed to the Personality module connector. Various options to select the SERDES clock configurations are present on the Personality modules. By default, SERDES reference clocks are generated internally and supplied on the REFCLK0P/N and REFCLK1P/N pins.

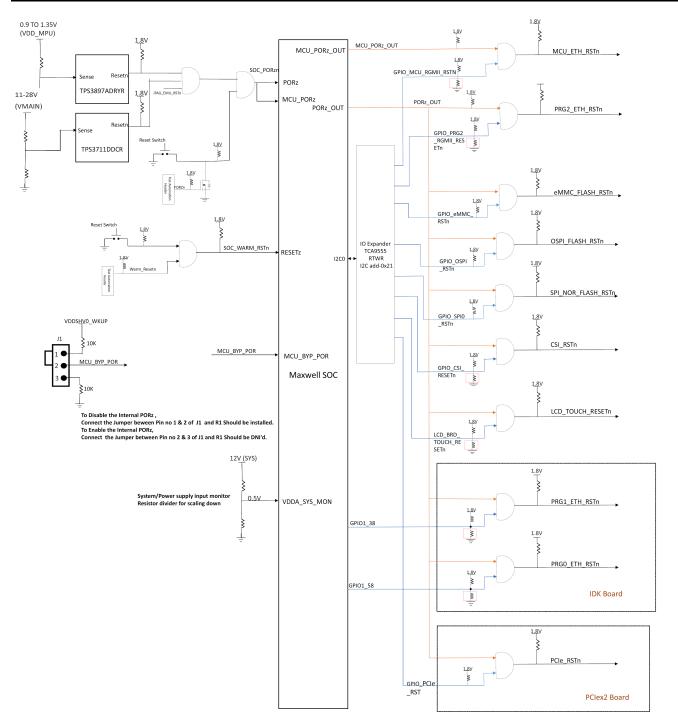

### 3.3.2 Reset

Warm reset input can be applied through manual reset switch SW7.

Power-on reset input can be applied though switch SW8.

The AM65x processor supports an option to bypass the internal POR generation. A 3-pin header J8 is provided to select internal or external POR. Short pin 2 and pin 3 of the header J8 to enable internal POR (default), and short pin 1 and 2 to bypass the internal POR.

Most peripheral resets are "ANDED" with the POR output from the SoC along with a GPIO control, as shown in Figure 3-5.

Figure 3-5. Overall Reset Architecture of the AM65x IDK

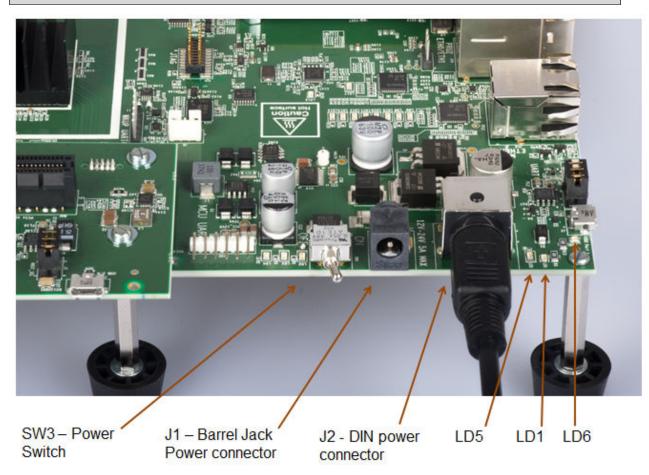

### 3.3.3 Power Requirements

### 3.3.3.1 Power Input

This IDK supports a wide input range of 11 V to 28 V. There are two connectors provided for power input:

- 4-pin DIN connector J2 which supports 10-A current rating

- DC barrel jack connector J1 which supports 5-A current rating

For most applications, the standard DC barrel jack can be used. The 4-pin DIN connector should be used when PCIe card is plugged in to the PCIe daughter card.

#### CAUTION

Never connect external power supplies to both the barrel jack and the din connectors at the same time.

Figure 3-6. Connectors Used for Power Input

#### 3.3.3.2 Overvoltage and Undervoltage Protection Circuit

The voltage protection circuit on the AM65x IDK protects the board from overvoltage, undervoltage, transient voltage, and reverse voltage input cases. The safe operation input voltage range is 11 V to 28 V. A fault indication and power good LEDs are provided to indicate the power status.

| LED | ON Status                       | OFF Status                        |

|-----|---------------------------------|-----------------------------------|

| LD1 | Power polarity reversed         | Power polarity good               |

| LD6 | Input voltage is >28 V or <11 V | Input voltage is within the limit |

| LD5 | Board Power on                  | Board Power off                   |

#### Table 3-2. Power LED Status

The power ON/OFF switch functionality is implemented using the over- and undervoltage protection circuit.

#### 3.3.3.3 Voltage Supervisor

The power rails are monitored to control the Power ON Reset (PORz) for SOC. Two supervisor devices are provided to monitor main power input and VDD\_MPU rail (last rail in the power on sequence of the SOC).

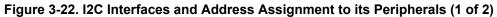

#### 3.3.3.4 Current Monitoring

INA226 power monitor devices are used to monitor current and voltage of various power rails of the AM65x processor. The device reports current, voltage, and power to the AM65x processor through the I2C interface. Four terminal high precision shunt resistors are provided, and the values are calculated based on load current.

| POWER SOURCE | SUPPLY NET   | SLAVE ADDRESS(IN HEX) | Value of the Shunt Connected to the Supply Rail |

|--------------|--------------|-----------------------|-------------------------------------------------|

| VCC1V0       | VDD_CORE     | 40                    | 0.002E_1%                                       |

| VCC1V0       | VDD_MCU      | 41                    | 0.01E_0.5%                                      |

| VCC3V3_IO    | VDD_MPU      | 42                    | 0.002E_1%                                       |

| SoC_MPU      | SoC_DVDD3V3  | 43                    | 0.002E_1%                                       |

| VCC1V8       | SoC_DVDD1V8  | 44                    | 0.01E_0.5%                                      |

| VDDA1V8      | SoC_AVDD1V8  | 45                    | 0.01E_0.5%                                      |

| VCC1V2_DDR   | SoC_VDDS_DDR | 46                    | 0.01E_0.5%                                      |

| VCC1V2_DDR   | VDD_DDR      | 47                    | 0.01E_0.5%                                      |

# Table 3-3. INA Devices I2C Slave Address

### 3.3.3.5 Power Supply

The processor card uses an array of DC-DC converters to supply the various memories, clocks, SOC, and other components on the card with the necessary voltage and the power required. Multiple power-good LEDs are provided on the card to give users positive confirmation of the status of output of each supply.

Test points for each power outputs are provided on the processor card and are mentioned in Table 3-4.

| Table | 3-4. | Power | Test | <b>Points</b> |

|-------|------|-------|------|---------------|

|-------|------|-------|------|---------------|

| SI #     | Power Supply  | Test Point | Voltage                                           | Tolerance    |

|----------|---------------|------------|---------------------------------------------------|--------------|

| Card Top | o Side        |            |                                                   |              |

| 1        | VINPUT        | TP10       | Applied input voltage                             | 11 V to 28 V |

| 2        | VMAIN         | TP9        | Applied input voltage                             | 11 V to 28 V |

| 3        | VCC_5V0       | TP7        | 5.0 V                                             | +/- 5%       |

| 4        | VCC3V3_PREREG | TP1        | 3.3 V                                             | +/- 5%       |

| 5        | VCC_12V0      | TP66       | 12.0 V                                            | +/- 5%       |

| 6        | VCC3V3_IO     | TP20       | 3.3 V                                             | +/- 5%       |

| 7        | VDDR_VTT      | TP5        | 1.65 V                                            | +/- 5%       |

| 8        | VCC_2V5       | TP82       | 2.5 V                                             | +/- 5%       |

| Card Bo  | ttom Side     | I          |                                                   |              |

| 1        | SoC_MPU       | TP24       | 1.0-V Typical, Changes based on I2C configuration | +/- 5%       |

| 2        | VCC1V2_DDR    | TP26       | 1.2 V                                             | +/- 5%       |

| 3        | VCC1V0        | TP25       | 1.0 V                                             | +/- 5%       |

| 4        | VPP_1V8       | TP23       | 1.8 V                                             | +/- 2.5%     |

| 5        | VDDA1V8       | TP22       | 1.8 V                                             | +/- 5%       |

| 6        | VDD_2V5       | TP64       | 2.5 V                                             | +/- 5%       |

| 7        | VDD_1V0       | TP27       | 1.0 V                                             | +/- 5%       |

| 8        | VCC1V8        | TP19       | 1.8 V                                             | +/- 5%       |

|      | Table 3-5. Power LEDs |     |  |  |  |

|------|-----------------------|-----|--|--|--|

| SI # | Power Supply          | LED |  |  |  |

| 1    | VCC3V3_PREREG         | LD3 |  |  |  |

| 2    | VCC_5V0               | LD2 |  |  |  |

| 3    | VCC_12V0              | LD4 |  |  |  |

# 3.3.3.6 Power Sequencing

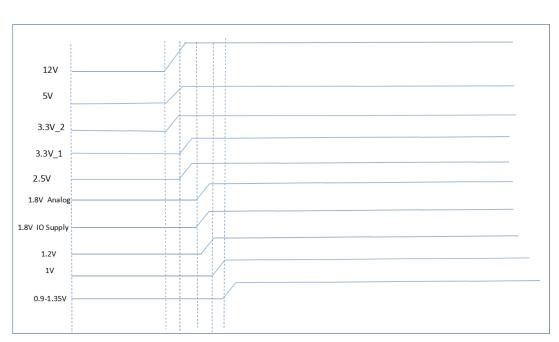

Figure 3-7 shows the power-up sequence of all the power supplies present on the processor card.

#### Power up Sequence

Power up Sequence: 12V, 5V,3.3V\_2 --->3.3V\_1, 2.5V --->1.8V Analog, 1.8V IO Supply ---> 1V SOC --->0.9-1.35V

There is no sequencing for 1V Peripheral supply

# Figure 3-7. Power ON Sequencing

#### 3.3.3.7 SoC Power

SoC has different I/O groups. Each I/O group is powered by specific power supplies, as shown in Table 3-6.

| SI.No. | Power Supply        | SoC Supply Rails | IO Power Group | Power |  |

|--------|---------------------|------------------|----------------|-------|--|

| 1      | VDDSHV_GENERAL      | VDDSHV0, VDDSHV1 | GENERAL        | 3.3 V |  |

| 2      | VDDSHV_GPMC         | VDDSHV2          | GPMC           | 3.3 V |  |

| 3      | VDDSHV_PRG0         | VDDSHV3          | PRG0           | 1.8 V |  |

| 4      | VDDSHV_PRG1         | VDDSHV4          | PRG1           | 1.8 V |  |

| 5      | VDDSHV_PRG2         | VDDSHV5          | PRG2           | 1.8 V |  |

| 6      | VDDSHV_MMC0         | VDDSHV6          | MMC0           | 1.8 V |  |

| 7      | VDDSHV_MMC1         | VDDSHV7          | MMC1           | 1.8 V |  |

| 8      | VDDSHV_WKUP_GENERAL | VDDSHV0_WKUP     | MCU_GENERAL    | 3.3 V |  |

#### Table 3-6. SOC Power Supply (continued)

| SI.No. | Power Supply       | SoC Supply Rails | IO Power Group | Power |  |  |

|--------|--------------------|------------------|----------------|-------|--|--|

| 9      | VDDSHV_WKUP_FLASH  | VDDSHV1_WKUP     | MCU_FLASH      | 1.8 V |  |  |

| 10     | VDDSHV_WKUP_CPSW2G | VDDSHV2_WKUP     | MCU_CPSW2G     | 1.8 V |  |  |

#### Table 3-7. SOC Bias Supply

| SI.No. | Bias Supply       | I/O Group   | Power                                     |

|--------|-------------------|-------------|-------------------------------------------|

| 1      | VDDS_GENERAL      | GENERAL     | Internal LDO (CAP_VDDA_1P8_IOLDO)         |

| 2      | VDDS_GPMC         | GPMC        | Internal LDO (CAP_VDDA_1P8_IOLDO)         |

| 3      | VDDS_PRG0         | PRG0        | 1.8-V I/O supply                          |

| 4      | VDDS_PRG1         | PRG1        | 1.8-V I/O supply                          |

| 5      | VDDS_PRG2         | PRG2        | 1.8-V I/O supply                          |

| 6      | VDDS_MMC0         | MMC0        | 1.8-V I/O supply                          |

| 7      | VDDS_MMC1         | MMC1        | 1.8-V I/O supply                          |

| 8      | VDDS_WKUP_GENERAL | MCU_GENERAL | Internal LDO<br>(CAP_VDDA_1P8_IOLDO_WKUP) |

| 9      | VDDS_WKUP_FLASH   | MCU_FLASH   | 1.8-V I/O supply                          |

| 10     | VDDS_WKUP_CPSW2G  | MCU_CPSW2G  | 1.8-V I/O supply                          |

# 3.3.4 Configuration

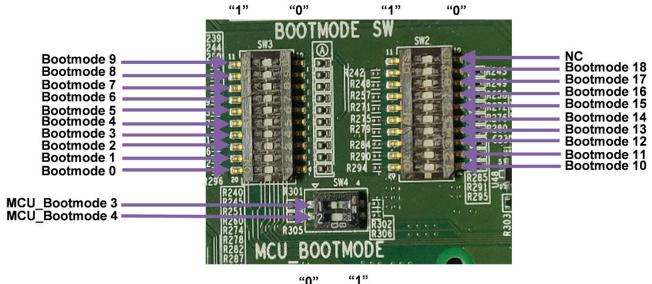

#### 3.3.4.1 Boot Modes

The boot mode for the SoC is defined by a bank of switches SW2, SW3, and SW4. Switch set to "ON" corresponds to logic "HIGH", while "OFF" corresponds to logic "LOW". The following boot modes are supported:

- 1. No boot

- 2. OSPI

- 3. MMC1 SDCard

- 4. MMC 0- eMMC installed

- 5. PCIE PCIE as an endpoint

- 6. CPSW Ethernet slave boot

- 7. USB boot using host mode with bulk storage. USB2.0 mass storage device using FAT16/32 (such as a thumb drive)

- 8. USB device boot DFU

- 9. UART

- 10.I2C EEPROM

The BOOTMODE pins provide the means to select the boot mode before the device is powered up. They are divided into the following categories.

|        |          |        | Bit 7                | Bit 6  | Bit 5   | Bit 4  | Bit 3  | Bit 2    | Bit 1   | Bit 0 |

|--------|----------|--------|----------------------|--------|---------|--------|--------|----------|---------|-------|

|        | _        |        | Min                  | Ba     | ckup Me | dia    | F      | rimary B | oot Med | ia    |

| Bit 18 | Bit 17   | Bit 16 | Bit 15               | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10   | Bit 9   | Bit 8 |

| Ba     | ckup Con | fig    | Primary Media Config |        |         |        |        |          |         |       |

#### Figure 3-8. BOOTMODE Bits

BOOTMODE[3:0] – This provides the primary boot mode configuration to select the requested boot mode after POR; that is, the peripheral/memory to boot from.

| SW3.4 | SW3.3 | SW3.2 | SW3.1 | Primary Boot Device Selected                                       |

|-------|-------|-------|-------|--------------------------------------------------------------------|

| off   | off   | off   | off   | Sleep (No boot – debug mode)                                       |

| off   | off   | off   | on    | OSPI                                                               |

| off   | off   | on    | off   | QSPI                                                               |

| off   | off   | on    | on    | Hyperflash                                                         |

| off   | on    | off   | off   | SPI (on QSPI/OSPI port 0 in legacy SPI mode)                       |

| off   | on    | off   | on    | 12C                                                                |

| off   | on    | on    | off   | MMC/SD card, eMMC boot from UDA or file system                     |

| off   | on    | on    | on    | Ethernet                                                           |

| on    | off   | off   | off   | USB                                                                |

| on    | off   | off   | on    | PCIe                                                               |

| on    | off   | on    | off   | UART                                                               |

| on    | off   | on    | on    | Reserved                                                           |

| on    | on    | off   | off   | GPMC XIP                                                           |

| on    | on    | off   | on    | eMMC boot from boot partition (with auto-fall back to file system) |

| on    | on    | on    | off   | Reserved (acts as no boot)                                         |

| on    | on    | on    | on    | Reserved (acts as no boot)                                         |

**•** • •

----

BOOTMODE[6:4] – Select the backup boot mode; that is, the peripheral/memory to boot from, if the primary boot device failed.

| SW3.6 | SW3.5                                                                                                                                 | Backup Boot Device Selected                                   |                                                                                                                                                                           |  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| off   | off                                                                                                                                   | off None (No backup mode)                                     |                                                                                                                                                                           |  |

| off   | on                                                                                                                                    | USB                                                           |                                                                                                                                                                           |  |

| on    | off                                                                                                                                   | UART                                                          |                                                                                                                                                                           |  |

| on    | on                                                                                                                                    | Ethernet                                                      |                                                                                                                                                                           |  |

| off   | off                                                                                                                                   | MMC/SD                                                        |                                                                                                                                                                           |  |

| off   | on                                                                                                                                    | SPI on OSPI/OSPI port 0 in legacy SPI mode)                   |                                                                                                                                                                           |  |

| on    | off                                                                                                                                   | Hyper flash                                                   |                                                                                                                                                                           |  |

| on    | on                                                                                                                                    | 12C                                                           |                                                                                                                                                                           |  |

|       | SW3.6       off       off       on       on       off       off       off       off       off       off       off       off       off | SW3.6SW3.5offoffoffonoffononoffononoffonoffoffoffonoffonoffon | SW3.6SW3.5Backup Boot Device SelectedoffoffNone (No backup mode)offonUSBonoffUARTononEthernetoffoffMMC/SDoffonSPI on OSPI/OSPI port 0 in legacy SPI mode)onoffHyper flash |  |

# Table 3-9. Backup Boot Mode Selection BOOTMODE[6:4]

BOOTMODE07 – This is the minimum (MIN) configuration pin. The min pin is provided as a way to use minimal pin strapping to configure boot. When the min pin value is 1, all configuration fields are based on pre-defined default values. In this case, no boot mode pins beyond the min pin need to be driven because their values are ignored.

BOOTMODE[15:8] – These pins provide optional settings and are used in conjunction with the primary boot device selected. Refer to the *AM65x Multicore ARM Keystone III System-on-Chip (SoC) Technical Reference Manual* for more details.

|          | Та                 | ble 3-10. Pri | mary Boot M     | Media Conf            | iguration B | DOTMODE[ | 15:8]      |             |  |     |

|----------|--------------------|---------------|-----------------|-----------------------|-------------|----------|------------|-------------|--|-----|

| SW2.6    | SW2.5              | SW2.4         | SW2.3           | SW2.2                 | SW2.1       | SW3.10   | SW3.9      | Boot Device |  |     |

|          | Not Used           |               |                 |                       |             |          |            |             |  |     |

|          | Pin Cmd            |               | C               | sel                   | S           | peed     | Adr Wid    | OSPI        |  |     |

| Port     | Pin                | Cmd           | С               | sel                   | S           | peed     | Adr Wid    | QSPI        |  |     |

| Not Used |                    |               |                 | Csel                  | 5           | Speed    | Hyperflash |             |  |     |

| Port     | M                  | ode           | C               | Csel Cmd Adr Width    |             | Csel     |            | Adr Width   |  | SPI |

| Not      | Not Used Bus Reset |               | Mode            | Spd                   | Addr        |          | I2C        |             |  |     |

|          | Not Used           | -             | Port            | Interface Config 1bit |             |          |            | MMC/SD card |  |     |

| cl       | kout               | ifa           | ace             | spd                   | dplx        | Ex       | tern con   | Ethernet    |  |     |

|          | Not                | Used          |                 | Usb3                  | N           | /lode    | Port       | USB         |  |     |

| Port     | Dual               | sref          | BAR Config PCIe |                       |             |          |            |             |  |     |

| Not      |                    |               |                 | Used                  |             |          |            | UART        |  |     |

| ldx      | AD                 | mux           | x Csel          |                       | (           | Csel     | Wid        | GPMC XIP    |  |     |

| Not Used | Port               | Alt           | Bus Width       |                       | S           | peed     | ack        | eMMC        |  |     |

BOOTMODE[18:16] – These pins provide optional settings and are used in conjunction with the backup boot device devices. Refer to the *AM65x Multicore ARM Keystone III System-on-Chip (SoC) Technical Reference Manual* for more information on bit details. Switches SW2.[7:9] when on sets 1 and sets 0 if off.

| Table 3-11. Backup Boot Media Configuration BOOTMODE[10:16] |        |             |          |  |

|-------------------------------------------------------------|--------|-------------|----------|--|

| SW2.9                                                       | SW2.8  | SW2.8 SW2.7 |          |  |

|                                                             | None   |             |          |  |

| No                                                          | t Used | Port        | USB      |  |

|                                                             | UART   |             |          |  |

| clkout                                                      | Inte   | rface       | Ethernet |  |

| Not Used                                                    | Port   | 1 Bit       | MMC/SD   |  |

| Port                                                        | Adr Wi | SPI         |          |  |

|                                                             | Sp     | Hyperflash  |          |  |

| reset                                                       | Mode   | Addr        | 12C      |  |

# Table 3-11. Backup Boot Media Configuration BOOTMODE[18:16]

MCU\_BOOTMODE pins provide ROM code with information for the system clock speed and fail-safe boot device.

#### Table 3-12. MCU BOOTMODE Bits

| Bit 10 | Bit 9    | Bit 8 | Bit 7 | Bit 6 | Bit 5    | Bit 4   | Bit 3 | Bit 2         | Bit 1 | Bit 0 |

|--------|----------|-------|-------|-------|----------|---------|-------|---------------|-------|-------|

|        | Reserved |       |       |       | Fail Saf | fe mode | R     | ef Clock Sele | ect   |       |

MCU\_BOOTMODE[2:0] – Denotes system clock frequency for PLL configuration. By default, these bits are set for 25 MHz.

#### Table 3-13. PLL Reference Clock Selection MCU\_BOOTMODE[2:0]

| Bit 2 | Bit 1 | Bit 0 | PLL REF CLK (MHz)                             |

|-------|-------|-------|-----------------------------------------------|

| 0     | 0     | 0     | 19.2                                          |

| 0     | 0     | 1     | 20                                            |

| 0     | 1     | 0     | 24                                            |

| 0     | 1     | 1     | 25                                            |

| 1     | 0     | 0     | 26                                            |

| 1     | 0     | 1     | 27                                            |

| 1     | 1     | 0     | Reserved                                      |

| 1     | 1     | 1     | No PLL Configuration Done (slow speed backup) |

# MCU\_BOOTMODE[4:3] – Select the fail-safe boot mode, as shown in Table 3-14.

| Table 3-14. Fail-Safe Boot Configuration |       |                             |  |  |

|------------------------------------------|-------|-----------------------------|--|--|

| SW4.2                                    | SW4.1 | PLL REF CLK (MHz)           |  |  |

| off                                      | off   | No fail-safe boot supported |  |  |

| off                                      | on    | 2C port 0                   |  |  |

| on                                       | off   | SPI Port 0                  |  |  |

| on                                       | on    | Hyperflash Port 0           |  |  |

# MCU\_BOOTMODE[10:5]- Reserved

"0"

# 3.3.4.2 JTAG

The common processor card includes XDS110 class on-card emulation through the micro B connector J23. It also has an optional TI20 pin (J13) connector to support external emulation. When an external emulator is connected, internal emulation circuitry is disabled. The design includes the footprint for a MIPI60pn (J32) connector with connections for JTAG and trace capabilities. The trace pins are pinmuxed with ICSSG2 RGMII signals which, by default, are connected to Ethernet PHYs on the processor board. Resistor networks are used to steer these signals to either the Ethernet PHYs or to the MIPI60 connector. The MIPI60 is not installed as delivered.

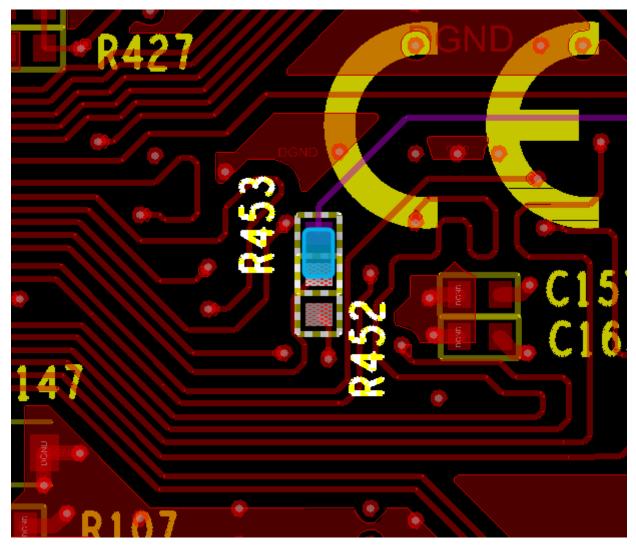

ICSSG2 Ethernet signals from the SoC are multiplexed with JTAG trace signals. Resistor options are provided to connect these signals to the Ethernet PHYs or Trace connector, as shown in Table 3-15.

| Signals selected                       | Mount | Un mount |

|----------------------------------------|-------|----------|

| PRG2 signals to Ethernet PHY (default) | RA3   | RA10     |

|                                        | RA5   | RA11     |

|                                        | RA1   | RA9      |

|                                        | R180  | R466     |

|                                        | R183  | R463     |

# Table 3-15. Selection of PRG2\_Ethernet PHY (CP Board PHY) and JTAG TRACE Functionality (continued)

| Signals selected          | Mount | Un mount |

|---------------------------|-------|----------|

| JTAG Trace signals to J32 | RA10  | RA3      |

|                           | RA11  | RA5      |

|                           | RA9   | RA1      |

|                           | R466  | R180     |

|                           | R463  | R183     |

### Table 3-16. TI20 Pin Connector (J13) Pin-out

| Pin No. | Signal         | Pin No. | Signal            |

|---------|----------------|---------|-------------------|

| 1       | JTAG_CTI_TMS   | 11      | СТІ_ТСК           |

| 2       | JTAG_TRSTN     | 12      | DGND              |

| 3       | JTAG_CTI_TDI   | 13      | JTAG_CTI_EMU0     |

| 4       | JTAG_TDIS      | 14      | JTAG_CTI_EMU1     |

| 5       | VCC3V3_CTI     | 15      | JTAG_CTI_EMU_RSTN |

| 6       | NC             | 16      | DGND              |

| 7       | JTAG_CTI_TDO   | 17      | NC                |

| 8       | SEL_XDS110_INV | 18      | NC                |

| 9       | CTI_RTCK       | 19      | NC                |

| 10      | DGND           | 20      | DGND              |

## Table 3-17. TI 60-pin Connector (J32) Pin-out

| Pin No. | Signal         | Pin No. | Signal             |

|---------|----------------|---------|--------------------|

| 1       | VCC3V3         | 31      | MIPI_TRC_DAT06     |

| 2       | MIPI_TMS       | 32      | NC                 |

| 3       | MIPI_TCK       | 33      | MIPI_TRC_DAT07     |

| 4       | MIPI_TDO       | 34      | NC                 |

| 5       | MIPI_TDI       | 35      | MIPI_TRC_DAT08     |

| 6       | MIPI_EMU_RSTn  | 36      | NC                 |

| 7       | MIPI_RTCK      | 37      | MIPI_TRC_DAT09     |

| 8       | MIPI_TRSTN     | 38      | JTAG_MIPI_EMU0_1V8 |

| 9       | NC             | 39      | MIPI_TRC_DAT10     |

| 10      | NC             | 40      | JTAG_MIPI_EMU1_1V8 |

| 11      | NC             | 41      | MIPI_TRC_DAT11     |

| 12      | VCC1V8_MIPI    | 42      | NC                 |

| 13      | MIPI_TRC_CLK   | 43      | MIPI_TRC_DAT12     |

| 14      | NC             | 44      | NC                 |

| 15      | DGND           | 45      | MIPI_TRC_DAT13     |

| 16      | DGND           | 46      | NC                 |

| 17      | MIPI_TRC_CTL   | 47      | MIPI_TRC_DAT14     |

| 18      | MIPI_TRC_DAT19 | 48      | NC                 |

| 19      | MIPI_TRC_DAT00 | 49      | MIPI_TRC_DAT15     |

| 20      | MIPI_TRC_DAT20 | 50      | NC                 |

| 21      | MIPI_TRC_DAT01 | 51      | MIPI_TRC_DAT16     |

| 22      | MIPI_TRC_DAT21 | 52      | NC                 |

| 23      | MIPI_TRC_DAT02 | 53      | MIPI_TRC_DAT17     |

| 24      | MIPI_TRC_DAT22 | 54      | NC                 |

| 25      | MIPI_TRC_DAT03 | 55      | MIPI_TRC_DAT18     |

| 26      | MIPI_TRC_DAT23 | 56      | NC                 |

| 27      | MIPI_TRC_DAT04 | 57      | DGND               |

| Pin No. | Signal         | Pin No. | Signal         |

|---------|----------------|---------|----------------|

| 28      | NC             | 58      | SEL_XDS110_INV |

| 29      | MIPI_TRC_DAT05 | 59      | NC             |

| 30      | NC             | 60      | NC             |

#### 3.3.4.2.1 Test Automation

A test automation header J41 is provided to allow an external controller to control the power on/off boot modes, reset functionality, and current measurement to support automated testing. The test automation header includes four GPIOs and two I2C interfaces. The basic controls are listed in Table 3-18.

| Signal     | Signal Type | Function                                             |

|------------|-------------|------------------------------------------------------|

| POWER_DOWN | GPIO        | Instructs the EVM to power down all circuits         |

| POR        | GPIO        | Creates a PORz into the Maxwell                      |

| WARM_RESET | GPIO        | Creates a RESETz into the Maxwell                    |

| GPIO1      | GPIO        | GPIO for communications with Maxwell                 |

| GPIO2      | GPIO        | GPIO for communications with Maxwell                 |

| GPIO3      | GPIO        | Used to Enable the BOOTMODE Buffer                   |

| GPIO4      | GPIO        | Used to Reset the Boot mode IO Expander              |

| 12C        | 12C         | Communicates with boot mode I2C buffer               |

| I2C2       | 12C         | Communicates with INA226 current measurement devices |

One of the I2C interfaces from the test automation header is connected to an I2C I/O expander, which can drive the boot mode pins of the processor. The bootmode selection switches should be in the OFF condition. GPIO3 should be set to logic low to enable this mode.

The other I2C interface is connected to the current measurement and temperature sensing devices present on the I2C2 port of the SoC.

The test automation connector is used by Texas Instruments to control the software regression testing and comparative power measurements. The connector is provided to allow customers to develop their own testing and power measurements of customer applications. Power measurements are not a substitute for the AM65x Power Estimation Tool and should not be used for the design of power supply solutions. Power measurements vary based on silicon process and environment, and measurements should only be used for comparison with other measurements taken on the same EVM.

| Table 3-19. Test Automation Header (J41) Pin-out |                  |                             |  |  |

|--------------------------------------------------|------------------|-----------------------------|--|--|

| Pin no.                                          | Signal           | I/O Direction (to CP Board) |  |  |

| 1                                                | VCC3V3_1         | Power (out)                 |  |  |

| 2                                                | VCC3V3_1         | Power (out)                 |  |  |

| 3                                                | VCC3V3_1         | Power (out)                 |  |  |

| 4                                                | NC               | NA                          |  |  |

| 5                                                | NC               | NA                          |  |  |

| 6                                                | NC               | NA                          |  |  |

| 7                                                | DGND             | Ground                      |  |  |

| 8                                                | NC               | NA                          |  |  |

| 9                                                | NC               | NA                          |  |  |

| 10                                               | NC               | NA                          |  |  |

| 11                                               | NC               | NA                          |  |  |

| 12                                               | NC               | NA                          |  |  |

| 13                                               | NC               | NA                          |  |  |

| 14                                               | NC               | NA                          |  |  |

| 15                                               | NC               | NA                          |  |  |

| 16                                               | DGND             | Ground                      |  |  |

| 17                                               | NC               | NA                          |  |  |

| 18                                               | NC               | NA                          |  |  |

| 19                                               | NC               | NA                          |  |  |

| 20                                               | NC               | NA                          |  |  |

| 21                                               | NC               | NA                          |  |  |

| 22                                               | NC               | NA                          |  |  |

| 23                                               | NC               | NA                          |  |  |

| 24                                               | NC               | NA                          |  |  |

| 25                                               | DGND             | Ground                      |  |  |

| 26                                               | TEST_POWERDOWN   | Input                       |  |  |

| 27                                               | TEST_PORZn       | Input                       |  |  |

| 28                                               | TEST_WARMRESETn  |                             |  |  |

| Input                                            |                  |                             |  |  |

| 29                                               | NC               | NA                          |  |  |

| 30                                               | TEST_GPIO1       | Bidirectional               |  |  |

| 31                                               | TEST_GPIO2       | Bidirectional               |  |  |

| 32                                               | TEST_GPIO3       | Input                       |  |  |

| 33                                               | TEST_GPIO4       | Input                       |  |  |

| 34                                               | DGND             | Ground                      |  |  |

| 35                                               | NC               | NA                          |  |  |

| 36                                               | SOC_I2C2_SCL     | Bidirectional               |  |  |

| 37                                               | BOOTMODE_I2C_SCL | Bidirectional               |  |  |

| 38                                               | SOC_I2C2_SDA     | Bidirectional               |  |  |

| 39                                               | BOOTMODE_I2C_SDA | Bidirectional               |  |  |

| 40                                               | DGND             | Ground                      |  |  |

| 41                                               | DGND             | Ground                      |  |  |

| 42                                               | DGND             | Ground                      |  |  |

# 3.3.4.3 UART Interface

Four UART ports of the SoC are interfaced with FT4232H for UART-to-USB functionality, and terminated on a micro B connector (J42) provided on the processor card. When the AM65x IDK is connected to a host using the provided USB cable, the computer can establish a virtual com port, which can be used with any terminal emulation application. The FT4232H is bus-powered. Virtual com port drivers for the FT4232H can be obtained from https://www.ftdichip.com/Products/ICs/FT4232H.htm.

Of the four UART ports of FT4232H, three are multiplexed; one with the application connector and the other two with test headers (J11 and J30). The control logic is given in Table 3-20.

| UART Port  | GPO Used From I2C Expander<br>(U82) | S0 | Selected Peripheral   |  |

|------------|-------------------------------------|----|-----------------------|--|

| MCU_UART0  | MCU_UART_SEL                        | L  | Test header           |  |

|            |                                     | Н  | FT4232                |  |

| WKUP_UART0 | WKUP_UART_SEL                       | L  | Test header           |  |

|            |                                     | Н  | FT4232                |  |

| MAIN_UART1 | MAIN_UART1_SEL                      | L  | FT4232                |  |

|            |                                     | Н  | Application connector |  |

#### Table 3-20. UART Selection Logic Table

The test headers (J11 and J30) pin out is given in Table 3-21.

### Table 3-21. UART Connectors (J11 and J30) Pin Out

| Pin No. | MCU_UART0 J30 | WKUP_UART0 J11 |

|---------|---------------|----------------|

| 1       | GND           | GND            |

| 2       | RTS           | RTS            |

| 3       | NC            | NC             |

| 4       | RX            | RX             |

| 5       | ТХ            | TX             |

| 6       | CTS           | CTS            |

# 3.3.5 Memory Interfaces

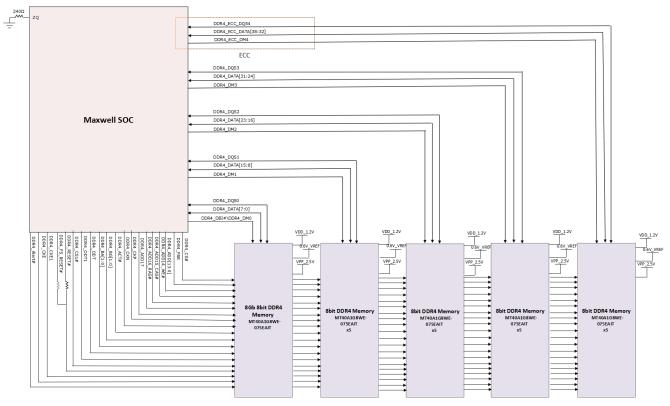

# 3.3.5.1 DDR4 Interface

The common processor board has 4 GB of DDR4 using four 8-Gb x8bit wide memory devices arranged in an 32bit wide bus. An additional 8-Gb x8bit wide memory device is provided to support seven bits of ECC. The DDR4 interface can operate up to 1600 MT/s speed. The DDR4 devices are connected using flyby routing for the address/command lines, and point-to-point connection for the data bus.

Figure 3-10. DDR4 Interface

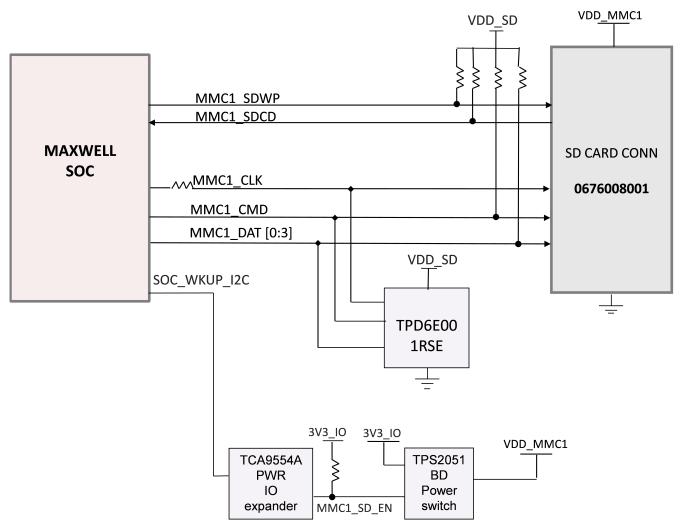

# 3.3.5.2 MMC Interface

The AM65x processor provides two MMC interfaces: one is connected to eMMC flash, and other is used for SD card interface.

### 3.3.5.2.1 SDHC Interface

The processor card provides an SD card interface through a connector J17, connected to the MMC1 port of the AM65x processor. The SD card interface supports UHS1 operation, including I/O operations at both 1.8 V and 3.3 V. The I/O voltage is controlled using the internal SDIO\_LDO, which provides the I/O voltage for the MMC1 port.

### 3.3.5.2.2 eMMC Interface

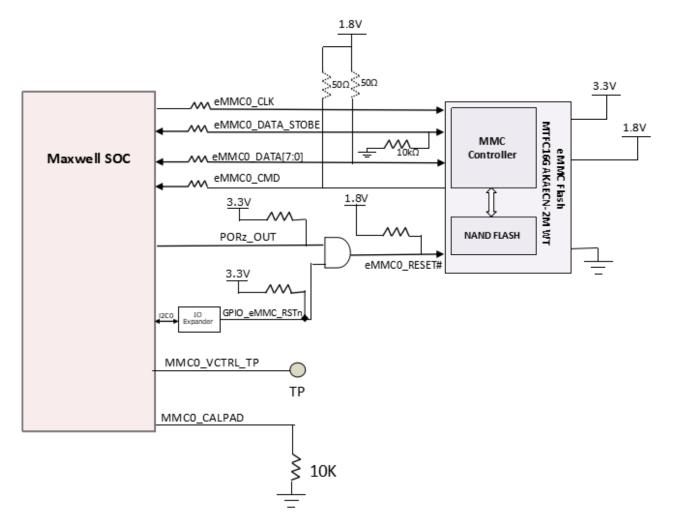

The processor card supports 16-GB eMMC flash memory (part number Micron MTFC16GAKAEJP-4M IT), connected to the MMC0 port of the AM65x processor. The flash is connected to 8bits of the MMC0 interface supporting HS400 double data rates up to 200 MHz.

Figure 3-12. eMMC Interface

# 3.3.5.3 OSPI Interface

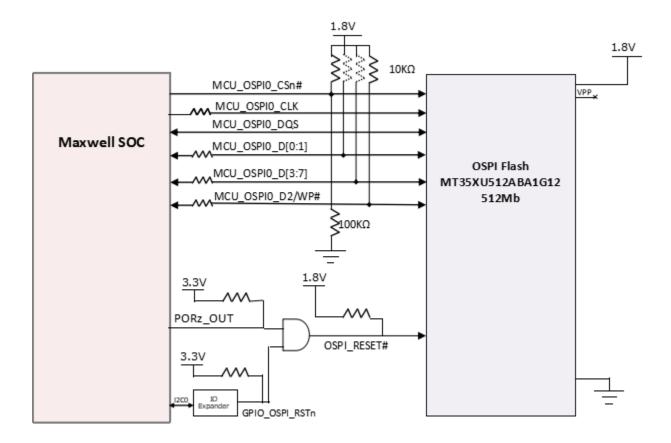

The processor card has a 512-Mbit OSPI memory device of part number MT35XU512ABA1G12-0SIT connected to the OSPI0 interface of the AM65x processor. The OSPI interface supports single and double data rates with memory speed up to 166-MHz SDR and 200-MHz DDR.

# Figure 3-13. OSPI Interface

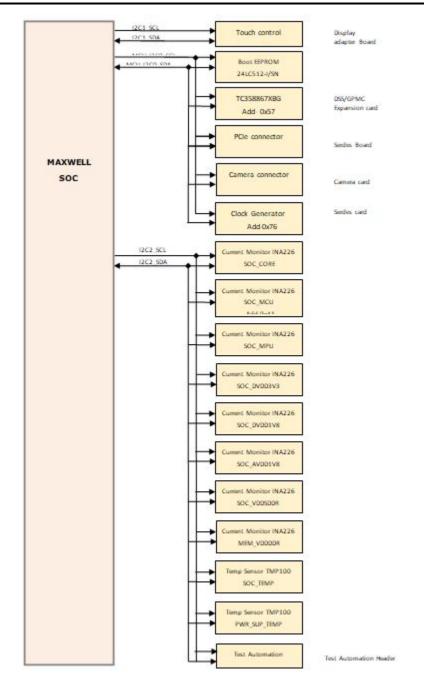

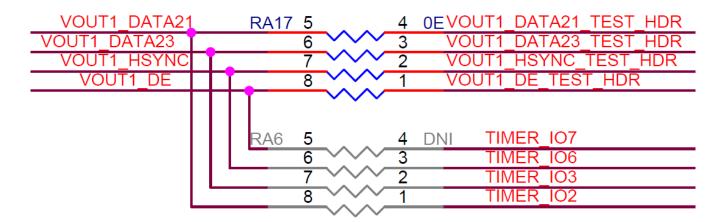

#### 3.3.5.4 SPI NOR Flash Interface

A 128-Mbit SPI NOR Flash of part number MT25QL128ABA8E12 is interfaced to the SPI0 port of the AM65x processor. In addition, SPI0 is also connected to the application connector and test automation header. SPI\_CS0 and SPI\_CS1 chip select signals are used for the serial flash and application connector, respectively.

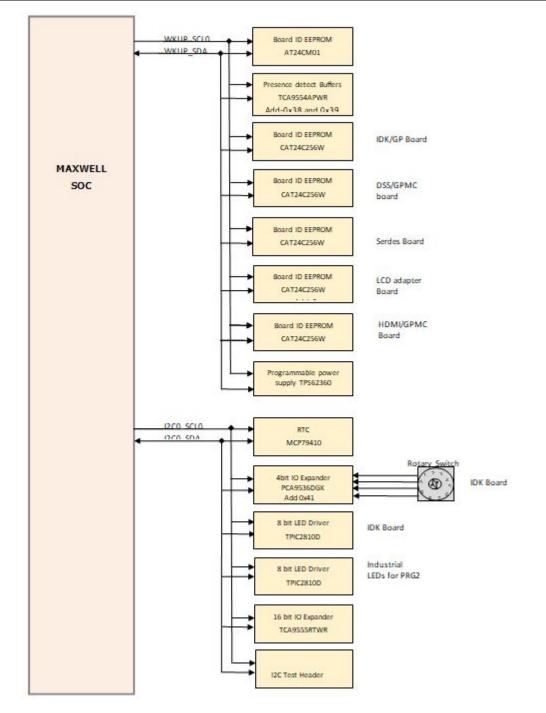

# 3.3.5.5 Board ID EEPROM Interface

The AM65x processor card is identified by its version and serial number, which are stored in the onboard EEPROM. The EEPROM is accessible on the address 0x50.

The AM65x CP board includes a CAT24C256W I2C EEPROM ID memory. The first 259 bytes of addressable EEPROM memory are preprogrammed with identification information for each board. The remaining 32509 bytes are available to the user for data or code storage.

| Header   | Field Name | Size (bytes) | Comments                                           |  |

|----------|------------|--------------|----------------------------------------------------|--|

| EE3355AA | MAGIC      | 4            | Magic number                                       |  |

|          | ТҮРЕ       | 1            | Fixed length and variable position board ID header |  |

|          |            | 2            | Size of payload                                    |  |

| BRD_INFO | TYPE       | 1            | payload type                                       |  |

|          | Length     | 2            | offset to next header                              |  |

#### Table 3-22. Board ID Memory Header Information

|          |             | Memory Header Inform |                                  |

|----------|-------------|----------------------|----------------------------------|

| Header   | Field Name  | Size (bytes)         | Comments                         |

|          | Board_Name  | 16                   | Name of the board                |

|          | Design_Rev  | 2                    | Revision number of the design    |

|          | PROC_Nbr    | 4                    | PROC number                      |

|          | Variant     | 2                    | Design variant number            |

|          | PCB_Rev     | 2                    | Revision number of the PCB       |

|          | SCHBOM_Rev  | 2                    | Revision number of the schematic |

|          | SWR_Rev     | 2                    | first software release number    |

|          | VendorID    | 2                    |                                  |

|          | Build_Week  | 2                    | week of the year of production   |

|          | Build_Year  | 2                    | year of production               |

|          | BoardID     | 6                    |                                  |

|          | Serial_Nbr  | 4                    | incrementing board number        |

| DDR_INFO | TYPE        | 1                    |                                  |

|          | Length      | 2                    | offset to next header            |

|          | DDR control | 2                    | DDR Control Word                 |

| MAC_ADDR | TYPE        | 1                    | payload type                     |

|          | Length      | 2                    | Size of payload                  |

|          | MAC control | 2                    | MAC header control word          |

|          | MAC_adrs    | 192                  | MAC adress of AM65x PRG2         |

| END_LIST | TYPE        | 1                    | End Marker                       |

# 3.3.5.6 Boot EEPROM Interface

A 256-Kbit EEPROM is interfaced to WKUP\_I2C for booting. Earlier versions of the board had this memory address set to 0x54. Later versions have the address set to 0x52.

# 3.3.6 Ethernet Interface

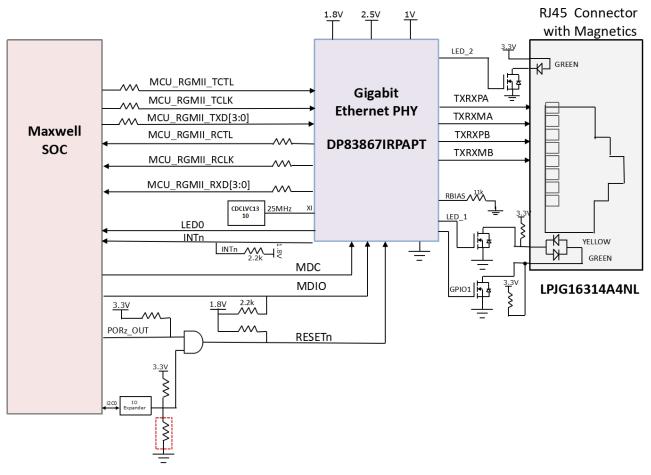

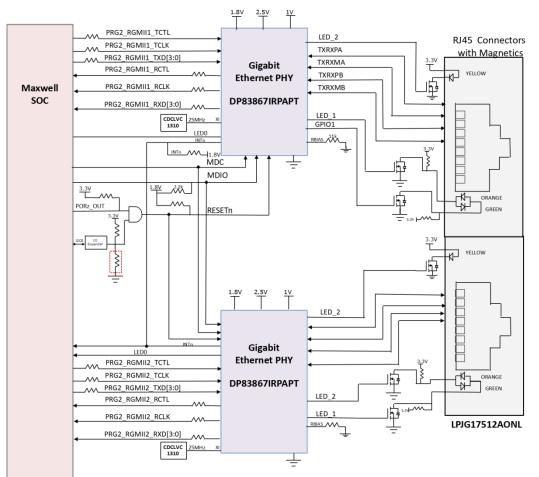

The AM65x EVM includes an RGMII connection between the DP83867 Gigabit Ethernet PHY and the network subsystem (NSS) of the processor. One RGMII interface (connected to RJ45 connector J12) from the MCU domain and two RGMII ports (connected to stacked RJ45 connector J14A and J14B) from ICSSG (PRG2) domain of the AM65x processor are used.

Figure 3-14. Ethernet Interface – MCU Domain

Figure 3-15. Ethernet Interface – ICSSG Domain

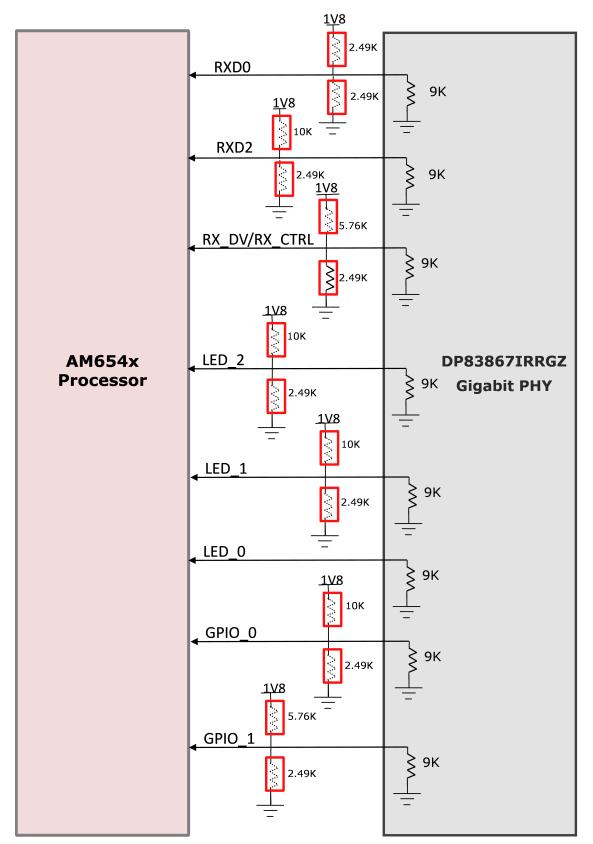

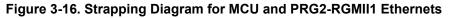

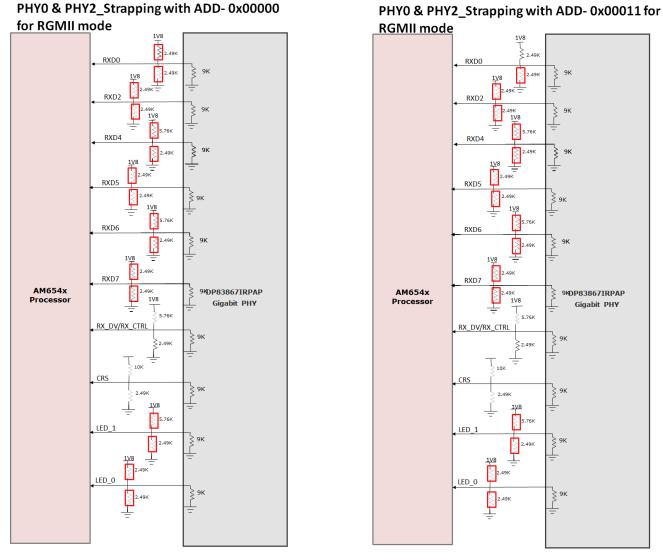

# 3.3.6.1 Gigabit Ethernet PHY Default Configuration

The default configuration of the DP83867 is determined using a number of resistor pull-up and pull-down values on specific pins of the PHY. Depending on the values installed, each of the configuration pins can be set to one of four modes by using the pull-up and pull-down options provided. The AM65x IDK uses the 48-pin QFN package, designated with the RGZ suffix, which only supports the RGMII interface.

The DP83867 PHY uses four level configurations based on resistor strapping, which generate four distinct voltage ranges. The resistors are connected to the RX data and control pins, which are normally driven by the PHY and are inputs to the processor. The voltage range for each mode is shown below:

Mode 1 - 0 V to 0.1764 V

Mode 2 - 0.252 V to 0.3438 V

Mode 3 – 0.405 V to 0.5112 V

Mode 4 – 1.2492 V to 1.5984 V

Default configurations of all phys are mentioned in Table 3-23.

|                           | Signal            | Mode |         |           | ing of Ethernet PHYs<br>Configuration                       | Description                                 |

|---------------------------|-------------------|------|---------|-----------|-------------------------------------------------------------|---------------------------------------------|

|                           |                   |      | Pull Up | Pull Down |                                                             |                                             |

| PRG2 RGMII1<br>PHY (J14A) | RX_D0             | 1    | Open    | Open      | PHY_AD1 = 0 and PHY_AD0<br>= 0                              | Address of the PHY is set to 00000          |

|                           | RX_D2             | 1    | Open    | Open      | PHY_AD3 = 0 and PHY_AD2<br>= 0                              |                                             |

|                           | RX_DV/<br>RX_CTRL | 1    | Open    | Open      | N/A                                                         | N/A                                         |

|                           | LED_2             | 1    | Open    | Open      | RGMII Clock Skew TX[1]=0<br>and RGMII Clock Skew<br>TX[0]=0 | RGMII Clock Skew TX = 2 ns<br>and advertise |

|                           | LED_1             | 1    | Open    | Open      | ANEG_SEL=0 and RGMII<br>Clock Skew TX[1]=0                  | -                                           |

|                           | GPIO_0            | 1    | Open    | Open      | RGMII Clock Skew RX[0]=0                                    | RGMII Clock Skew RX = 2 ns                  |

|                           | GPIO_1            | 1    | Open    | Open      | RGMII Clock Skew RX[2]=0<br>and RGMII Clock Skew<br>RX[1]=0 |                                             |

| PRG2 RGMII1<br>PHY (J14B) | RX_D0             | 4    | 2.49K   | Open      | PHY_AD1 = 1 and PHY_AD0<br>= 1                              | Address of the PHY is set to 00011          |

|                           | RX_D2             | 1    | Open    | Open      | PHY_AD3 = 0 and PHY_AD2<br>= 0                              | _                                           |

|                           | RX_DV/<br>RX_CTRL | 1    | Open    | Open      | N/A                                                         | N/A                                         |

|                           | LED_2             | 1    | Open    | Open      | RGMII Clock Skew TX[1]=0<br>and RGMII Clock Skew<br>TX[0]=0 | RGMII Clock Skew TX = 2 ns<br>and advertise |

|                           | LED_1             | 1    | Open    | Open      | ANEG_SEL=0 and RGMII<br>Clock Skew TX[1]=0                  |                                             |

|                           | GPIO_0            | 1    | Open    | Open      | RGMII Clock Skew RX[0]=0                                    | RGMII Clock Skew RX = 2 ns                  |

|                           | GPIO_1            | 1    | Open    | Open      | RGMII Clock Skew RX[2]=0<br>and RGMII Clock Skew<br>RX[1]=0 |                                             |

| PRG2 RGMII1<br>PHY (J12)  | RX_D0             | 1    | Open    | Open      | PHY_AD1 = 0 and PHY_AD0<br>= 0                              | Address of the PHY is set to 00000          |

|                           | RX_D2             | 1    | Open    | Open      | PHY_AD3 = 0 and AN2 = 0                                     |                                             |

|                           | RX_DV/<br>RX_CTRL | 1    | Open    | Open      | N/A                                                         | N/A                                         |

|                           | LED_2             | 1    | Open    | Open      | RGMII Clock Skew TX[1]=0<br>and RGMII Clock Skew<br>TX[0]=0 | RGMII Clock Skew TX = 2 ns<br>and advertise |

|                           | LED_1             | 1    | Open    | Open      | ANEG_SEL=0 and RGMII<br>Clock Skew TX[1]=0                  |                                             |

|                           | GPIO_0            | 1    | Open    | Open      | RGMII Clock Skew RX[0]=0                                    | RGMII Clock Skew RX = 2 ns                  |

|                           | GPIO_1            | 1    | Open    | Open      | RGMII Clock Skew RX[2]=0<br>and RGMII Clock Skew<br>RX[1]=0 |                                             |

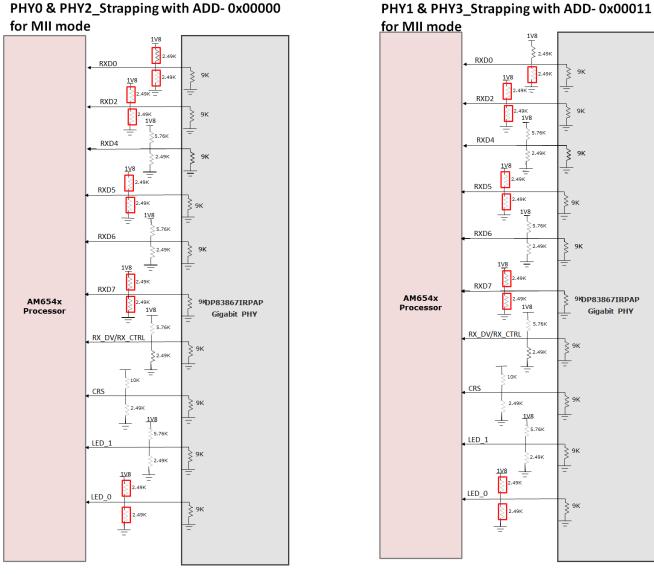

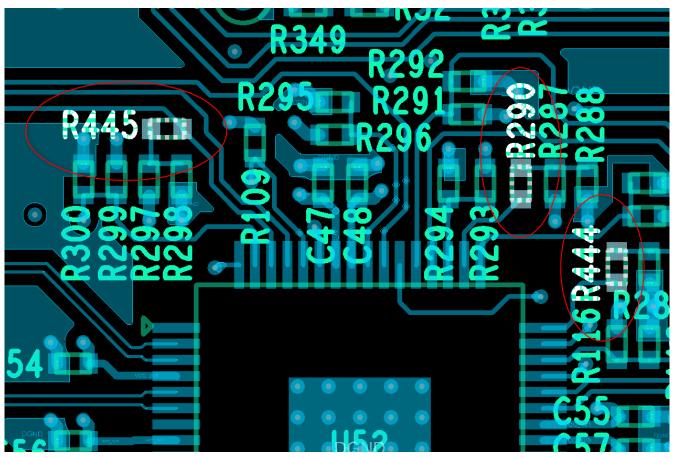

Figure 3-17. Strapping Diagram for PRG2-RGMII2 Ethernet

#### Note

Resistors which are highlighted in red color boxes are DNI components.

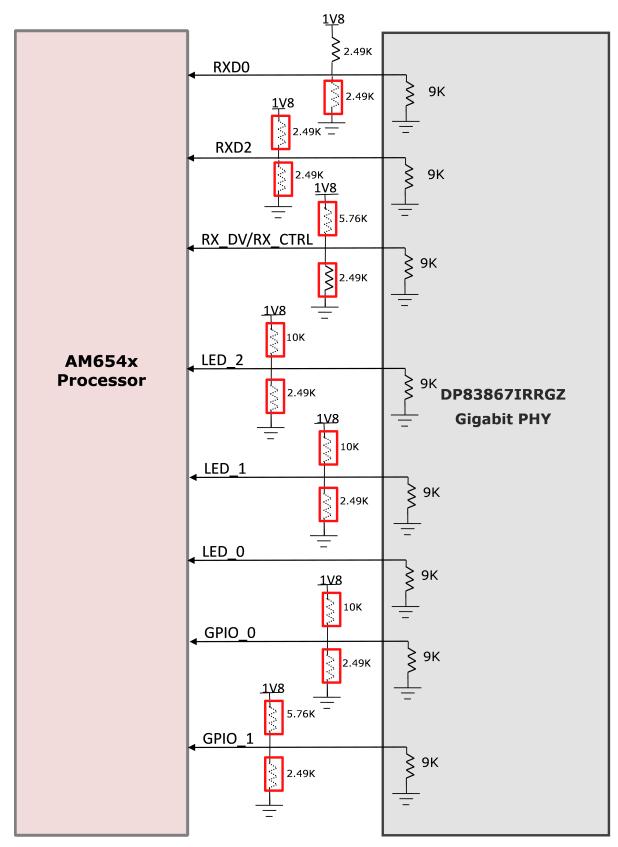

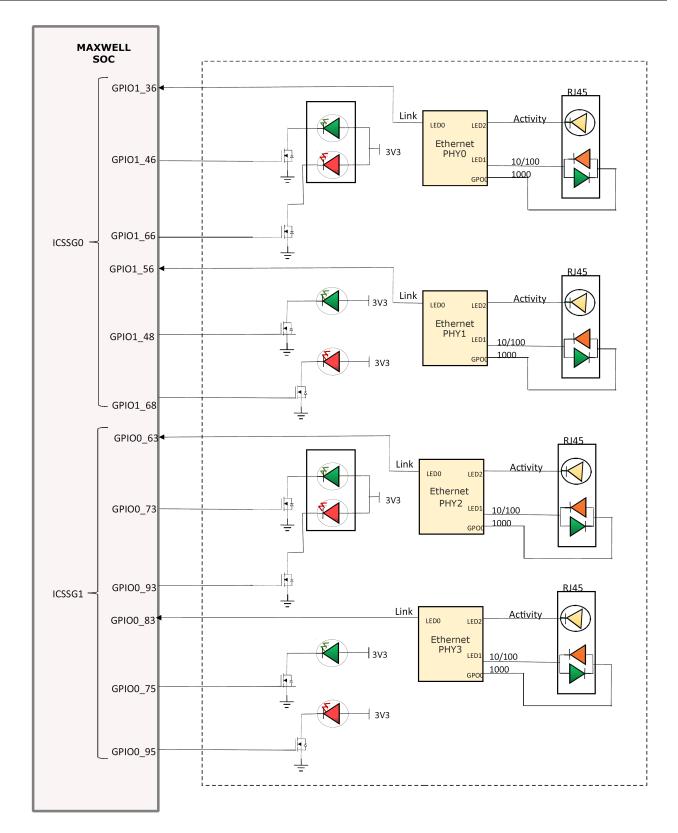

### 3.3.6.2 Ethernet LEDs

The common processor card has LEDs to indicate the status of the Ethernet link. Some of the LEDs on the CP board are used for industrial applications; those can be controlled with I2C0 of the processor, which is connected to an I/O expander and some processor GPOs.

From the Ethernet PHY, LED1 and GPIO0 are connected to dual LEDs of RJ45 to indicate a 10/100-Mb or 1000-Mb link. The green LED indicates 10/100-Mb speed, and the orange LED indicates 1000-Mb speed.

LED2 is connected to RJ45 LED (Yellow) to indicate transmit/receive activity.

Figure 3-18. CP Board Ethernet Interface – LEDs

# 3.3.7 LCD Display Interface

The processor board provides a common display interface terminated to the I-PEX connector J38 of part number 20720-040E-02. It is a 0.5-mm pitch Shielded FFC / FPC connector. The PWM output signal from the AM65x processor is terminated to the I-PEX connector, which is used to drive the back-light circuit in the adapter card.

| Pin no. | Signal                  | Direction     |  |

|---------|-------------------------|---------------|--|

| 1       | VCC_5V0                 | Power         |  |

| 2       | VCC_5V0                 | Power         |  |

| 3       | VCC_5V0                 | Power         |  |

| 4       | VCC3V3_IO               | Power         |  |

| 5       | VCC3V3_IO               | Power         |  |

| 6       | DGND                    | Power         |  |

| 7       | DGND                    | Power         |  |

| 8       | OLDI0_A0N               | Output        |  |

| 9       | OLDI0_A0P               | Output        |  |

| 10      | DGND                    | Power         |  |

| 11      | OLDI0_A1N               | Output        |  |

| 12      | OLDI0_A1P               | Output        |  |

| 13      | DGND                    | Power         |  |

| 14      | OLDI0_A2N               | Output        |  |

| 15      | OLDI0_A2P               | Output        |  |

| 16      | DGND                    | Power         |  |

| 17      | OLDI0_A3N               | Output        |  |

| 18      | OLDI0_A3P               | Output        |  |

| 19      | DGND                    | Power         |  |

| 20      | OLDI0_CLKN              | Output        |  |

| 21      | OLDI0_CLKP              | Output        |  |

| 22      | DGND                    | Power         |  |

| 23      | SOC_WKUP_SCL            | Output        |  |

| 24      | SOC_WKUP_SDA            | Bidirectional |  |

| 25      | DGND                    | Power         |  |

| 26      | SOC_I2C1_SCL            | Output        |  |

| 27      | SOC_I2C1_SDA            | Bidirectional |  |

| 28      | DGND                    | Power         |  |

| 29      | LCD_BRD_TOUCH_INT       | Input         |  |

| 30      | LCD_DISPLAY_EN/BRD_RSTN | Output        |  |

| 31      | CARD ID_LCD_A0          | Output        |  |

| 32      | SOC_SPI1_CLK            | Output        |  |

| 33      | SOC_SPI1_CS0            | Output        |  |

| 34      | CARD ID_LCD_A1          | Output        |  |

| 35      | SOC_SPI1_MOSI           | Output        |  |

| 36      | SOC_SPI1_MISO           | Input         |  |

| 37      | CARD ID_LCD_A2          | Output        |  |

| 38      | ECAP0_IN_APWM0_OUT      | Output        |  |

| 39      | LCD_TOUCH_RESETN        | Output        |  |

| 40      | LCD_BRD_DET             | Input         |  |

#### Table 3-24. Display Connector (J38) Pin-out

# 3.3.8 USB 2.0 Interface

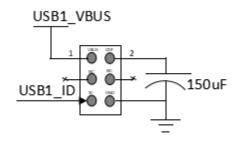

The SoC supports two USB 2.0 ports – USB0 and USB1. The USB0 port is routed to the SERDES daughter card connector along with USB0 ID pins and DRVVBUS0 for host / slave detect and power enable. The USB1 port is terminated to a uAB connector (J3) and supports both host and slave mode. In the host mode, up to 500 mA, 5 V is supported for the slave device. A power switch is included which is controlled by DRV\_VBUS signal from the AM65x processor. A 2x3 header (J4) is provided to install the 2-position ganged shunt to configure the port for host mode, as shown in Figure 3-19. Place the shunt on pin 1 and 2 to enable bulk capacitance on VBUS, and place the shunt on pin 5 and 6 to connect ID pin to ground.

Figure 3-19. J4 Header for USB2.0 Host Interface

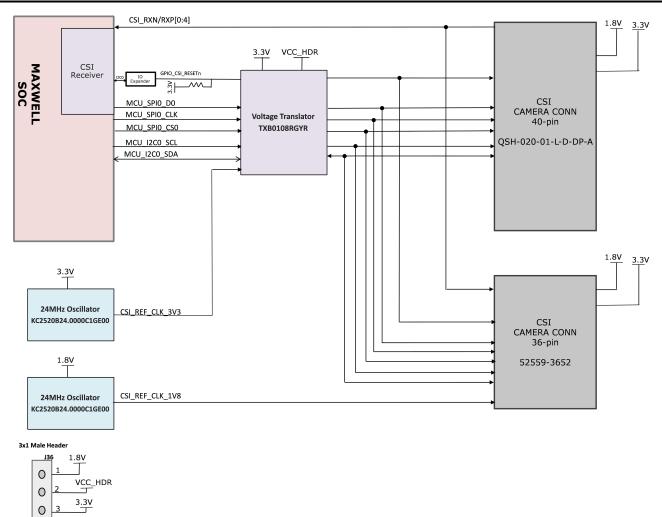

### 3.3.9 CSI-2 Interface

The CSI-2 interface from the AM65x processor is terminated to two camera connectors to interface a CSI-2 standard camera:

- J22 40-pin Samtec connector, which is referenced from OV490 / OV10640 Combo Module

- J39 36-pin Molex connector, which is referred from Leopard Imaging CPI (VIN) Connector

The two connectors match the existing standards for camera cards. The CSI-2 connector on the board is selected based on the camera module installed. MCU\_I2C0 and MCU\_SPI0 are also connected to the camera connector through level translators.

The control signals connected to J39 are all 1.8 V, whereas the control signals connected to J22 can be either 1.8 V or 3.3 V. A jumper (J37) is used to select the required I/O voltage, as shown in Figure 3-20. Short Pin 1 and Pin 2 for 1.8-V I/O operation, or Short Pin 2 and Pin 3 for 3.3-V I/O operation. The footprint to mount the oscillator of part number KC2520B24.0000C1GE00 is provided to supply 24-MHz REFCLK to the CSI-2 module. Mount U114 for 1.8-V REFCLK, and mount U112 for 3.3-V REFCLK.

Jumper to select the IO level of CSI connector

-

| Figure | 3-20. | CSI | Interface |

|--------|-------|-----|-----------|

|--------|-------|-----|-----------|

| Table 3-25. CSI-2 Samtec Connector | (J22 | ) Pin-out |

|------------------------------------|------|-----------|

|------------------------------------|------|-----------|

| Pin Number | CP Card Signals-CSI | Direction     |

|------------|---------------------|---------------|

| 1          | NC                  | NA            |

| 2          | CSI_MCU_SCL         | Output        |

| 3          | NC                  | NA            |

| 4          | CSI_MCU_SDA         | Bidirectional |

| 5          | CSI0_RXP0           | Input         |

| 6          | NC                  | NA            |

| 7          | CSI0_RXN0           | Input         |

| 8          | NC                  | NA            |

| 9          | CSI0_RXP1           | Input         |

| 10         | CSI_REF_CLK         | Output        |

| 11         | CSI0_RXN1           | Input         |

| 12         | DGND                | Power         |

| 13         | CSI0_RXP2           | Input         |

| 14         | CSI_RESETN          | Output        |

| 15         | CSI0_RXN2           | Input         |

| 16         | DGND                | Power         |

| Pin Number | CP Card Signals-CSI | Direction |

|------------|---------------------|-----------|

| 17         | CSI0_RXP3           | Input     |

| 18         | CSI_MCU_SPI0_D0     | Output    |

| 19         | CSI0_RXN3           | Input     |

| 20         | CSI_MCU_SPI0_CLK    | Output    |

| 21         | CSI0_RXP4           | Input     |

| 22         | CSI_MCU_SPI0_CS0    | Output    |

| 23         | CSI0_RXN4           | Input     |

| 24         | DGND                | Power     |

| 25         | NC                  | NA        |

| 26         | NC                  | NA        |

| 27         | NC                  | NA        |

| 28         | NC                  | NA        |

| 29         | NC                  | NA        |

| 30         | VCC3V3_IO           | Power     |

| 31         | NC                  | NA        |

| 32         | VCC3V3_IO           | Power     |

| 33         | NC                  | NA        |

| 34         | VCC3V3_IO           | Power     |

| 35         | NC                  | NA        |

| 36         | VCC3V3_IO           | Power     |

| 37         | NC                  | NA        |

| 38         | VCC1V8              | Power     |

| 39         | NC                  | NA        |

| 40         | VCC1V8              | DGND      |

#### Table 3-25. CSI-2 Samtec Connector (J22) Pin-out (continued)

### Table 3-26. CSI-2 Molex Connector (J39) Pin-out

| Pin Number | CP Card Signals-CSI | Direction |

|------------|---------------------|-----------|

| 1          | VCC3V3_IO           | Power     |

| 2          | VCC3V3_IO           | Power     |

| 3          | VCC3V3_IO           | Power     |

| 4          | VCC1V8              | Power     |

| 5          | VCC1V8              | Power     |

| 6          | DGND                | DGND      |

| 7          | DGND                | NC        |

| 8          | CSI0_RXP0           | Input     |

| 9          | CSI0_RXN0           | Input     |

| 10         | DGND                | Power     |

| 11         | CSI0_RXP1           | Input     |

| 12         | CSI0_RXN1           | Input     |

| 13         | DGND                | Power     |

| 14         | CSI0_RXP2           | Input     |

| 15         | CSI0_RXN2           | Input     |

| 16         | DGND                | Power     |

| 17         | CSI0_RXP3           | Input     |

| 18         | CSI0_RXN3           | Input     |

| 19         | DGND                | Power     |

| 20         | CSI0_RXP4           | Input     |

| Pin Number | CP Card Signals-CSI | Direction     |

|------------|---------------------|---------------|

| 21         | CSI0_RXN4           | Input         |

| 22         | DGND                | Power         |

| 23         | CSI_RESETN          | Output        |

| 24         | CSI_MCU_SDA         | Bidirectional |

| 25         | CSI_MCU_SCL         | Output        |

| 26         | CSI_REF_CLK_1V8     | Output        |

| 27         | NC                  | NA            |

| 28         | NC                  | NA            |

| 29         | DGND                | Power         |

| 30         | CSI_MCU_SPI0_D0     | Output        |

| 31         | CSI_MCU_SPI0_CLK    | Output        |

| 32         | CSI_MCU_SPI0_CS0    | Output        |

| 33         | DGND                | Power         |

| 34         | DGND                | Power         |

| 35         | NC                  | NA            |

| 36         | NC                  | NA            |

# Table 3-26, CSL-2 Molex Connector (139) Pin-out (continued)

#### 3.3.10 Application Card Interface

The common processor card includes an application connector to interface different pin-multiplexed functions of the PRG0 and PRG1 I/O groups of the AM65x processor. The main purpose of the application card is to highlight the industrial capabilities of the AM65x processor. All the signals associated with the PRG0 and PRG1 interface are routed to the application connector.

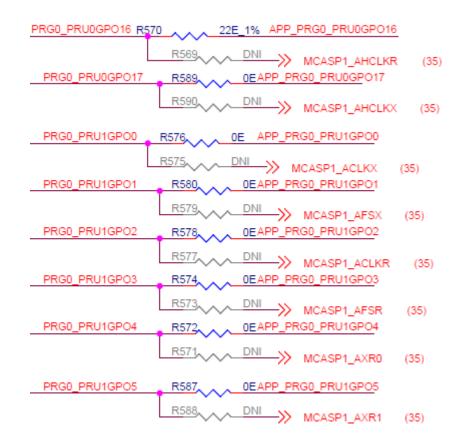

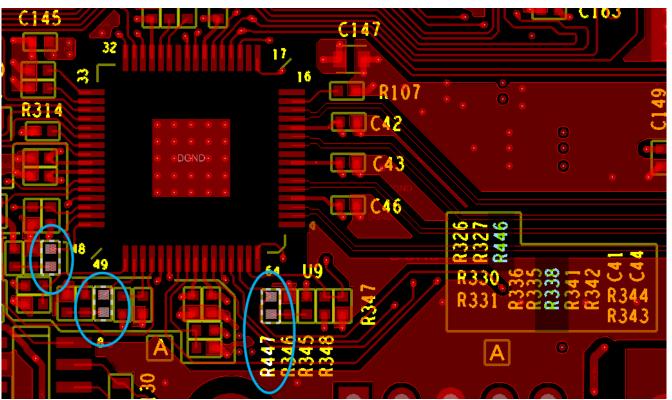

The interfaces provided on the application connector are RGMII, UART, MCAN, I2C, SPI, McASP, ADC, and PWM signals. The PRG0 signals are multiplexed with the McASP1 signals of the HDMI/GPMC card. Resistor options are provided to allow for the selection of the required interface, as shown in Figure 3-21. Table 3-27 lists the resistors that are mounted or demounted to select RGMII signals on the application connector.

| Refdes | Application Connector | HDMI/GPMC Expansion Connector |

|--------|-----------------------|-------------------------------|

| R570   | Mount                 | DNI                           |

| R589   | Mount                 | DNI                           |

| R576   | Mount                 | DNI                           |

| R580   | Mount                 | DNI                           |

| R578   | Mount                 | DNI                           |

| R574   | Mount                 | DNI                           |

| R572   | Mount                 | DNI                           |

| R587   | Mount                 | DNI                           |

| R569   | DNI                   | Mount                         |

| R590   | DNI                   | Mount                         |

| R575   | DNI                   | Mount                         |

| R579   | DNI                   | Mount                         |

| R577   | DNI                   | Mount                         |

| R573   | DNI                   | Mount                         |

| R571   | DNI                   | Mount                         |

| R588   | DNI                   | Mount                         |

#### Table 3-27. Selection of PRG0 Signals on the Application Connector

#### Figure 3-21. Multiplexed RGMII/McASP1 Signal Selection

The card presence detect signal from the application card is connected to the I/O expander, which in turn is connected to the WKUP I2C0 port of the AM65x processor.

The 120-pin connector pin-out is given in Table 3-28.

| Pin Number | CP Card Signals      | IDK Card Signals    | Direction |  |

|------------|----------------------|---------------------|-----------|--|

| 1          | DGND                 | DGND                | Power     |  |

| 2          | DGND                 | DGND                | Power     |  |

| 3          | PRG1_RGMII1_ETH1_CLK | ETH0_CLK            | Output    |  |

| 4          | PRG0_RGMII1_ETH1_CLK | ETH1_CLK            | Output    |  |

| 5          | DGND                 | DGND                | Power     |  |

| 6          | DGND                 | DGND                | Power     |  |

| 7          | PRG0_PRU0GPO15       | ETH0_RGMII_TD3      | Output    |  |

| 8          | APP_PRG0_PRU1GPO5    | NC                  | NA        |  |

| 9          | PRG0_PRU0GPO13       | ETH0_RGMII_TD1      | Output    |  |

| 10         | APP_PRG0_PRU0GPO17   | ETH_LED1            | Output    |  |

| 11         | PRG0_PRU0GPO14       | ETH0_RGMII_TD2      | Output    |  |

| 12         | PRG0_PRU0GPO19       | ETH_LED3            | Output    |  |

| 13         | PRG0_PRU0GPO11       | ETH0_RGMII_TX_CTL   | Output    |  |

| 14         | PRG0_PRU0GPO18       | PRG0_IEP0_LATCH_IN0 | Input     |  |

| 15         | PRG0_PRU0GPO12       | ETH0_RGMII_TD0      | Output    |  |

| 16         | PRG0_PRU0GPO7        | ETH0_LED_LINK       | Input     |  |

| 17         | DGND                 | DGND                | Power     |  |

Table 3-28. 120-pin Application Connector (J18) Pin-out

| Table 3-28. 120-pin Application Connector (J18) Pin-out (continued) |                    |                     |               |

|---------------------------------------------------------------------|--------------------|---------------------|---------------|

| Pin Number                                                          | CP Card Signals    | IDK Card Signals    | Direction     |

| 18                                                                  | PRG0_PRU0GPO10     | ETH0/1_INTN         | Input         |

| 19                                                                  | APP_PRG0_PRU0GPO16 | ETH0_RGMII_TXC      | Output        |

| 20                                                                  | PRG0_PRU0GPO8      | NC                  | NA            |

| 21                                                                  | DGND               | DGND                | Power         |

| 22                                                                  | PRG0_PRU1GPO8      | NC                  | NA            |

| 23                                                                  | PRG0_PRU0GPO3      | ETH0_RGMII_RD3      | Input         |

| 24                                                                  | PRG0_PRU1GPO17     | ETH_LED2            | Output        |

| 25                                                                  | DGND               | DGND                | Power         |

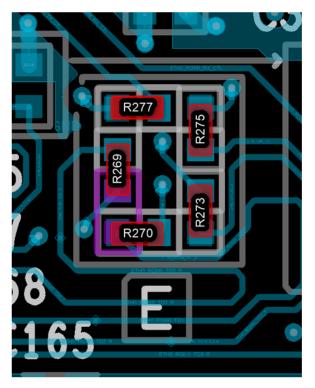

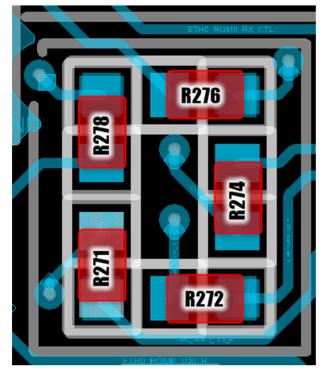

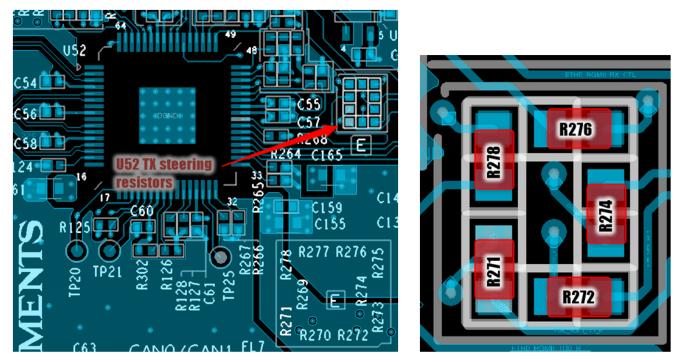

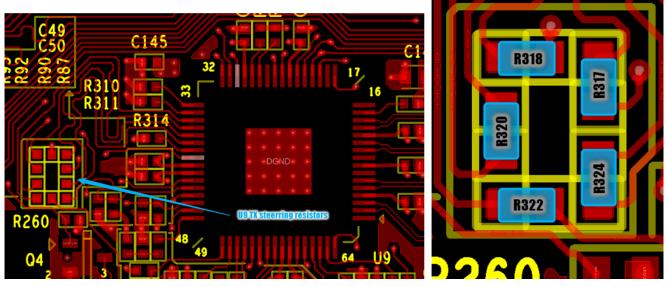

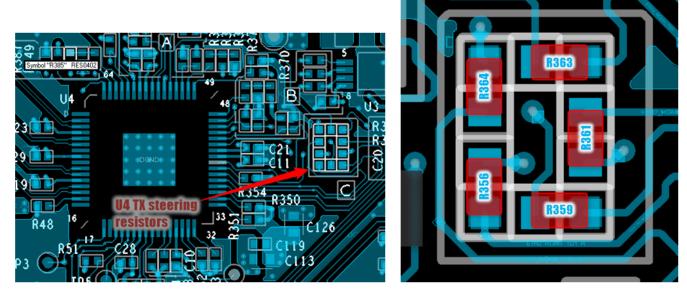

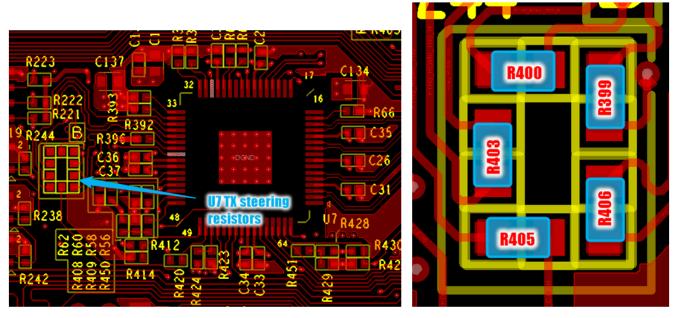

| 26                                                                  | APP_PRG0_PRU1GPO4  | ETH1_RGMII_RX_CTL   | Input         |